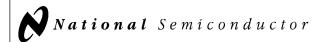

## LH0032 Ultra Fast FET-Input Operational Amplifier

### **General Description**

The LH0032 is a high slew rate, high input impedance differential operational amplifier suitable for diverse applications in fast signal handling. The high allowable differential input voltage, ease of output clamping, and high output drive capability particularly suit it for comparator applications. It may be used in applications normally reserved for video amplifiers allowing the use of operational gain setting and frequency response shaping into the megahertz region.

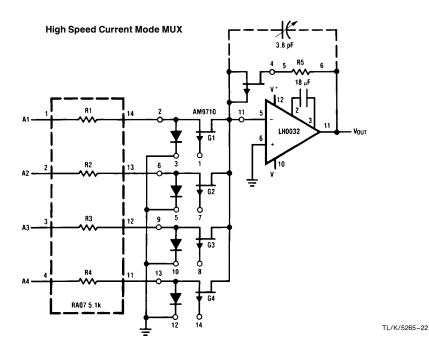

The LH0032's wide bandwidth, high input impedance and high output capacity make it an ideal choice for applications such as summing amplifiers in high speed D to A converters, buffers in data acquisition systems and sample and hold circuits. Additional applications include high speed integrators and video amplifiers. The LH0032 is guaranteed for operation over the temperature range  $-55^\circ\mathrm{C}$  to  $+125^\circ\mathrm{C}$ , the LH0032C is guaranteed for  $-25^\circ\mathrm{C}$  to  $+85^\circ\mathrm{C}$ .

#### **Features**

- 500 V/µs slew rate

- 70 MHz bandwidth

- $10^{12}\Omega$  input impedance

- As low as 2 mV max input offset voltage

- FET input

- Peak output current to 100 mA

### **Absolute Maximum Ratings** (Note 9)

Supply Voltage,  $V_S$ Input Voltage, V<sub>IN</sub>  $\pm V_S$  $\pm\,30V$  or  $\pm\,2V_{\mbox{\scriptsize S}}$ Differential Input Voltage Power Dissipation, PD (Note 10)

Steady State Output Current  $\pm\,100~mA$ -65°C to +150°C Storage Temperature Range

Lead Temp. (Soldering, 10 seconds) 300°C

## **Operating Ratings**

Temperature Range, T<sub>A</sub> LH0032G

$-55^{\circ}\text{C to } + 125^{\circ}\text{C}$ LH0032CG -25°C to +85°C

Junction Temperature, T<sub>J</sub> LH0032G

Thermal Resistance (Note 8)  $\theta_{\rm JA}$  G Package 100°C/W 70°C/W  $\theta_{JC}$  G Package

+175°C

# $\textbf{DC Electrical Characteristics} \ \ V_S = \ \pm \ 15 \text{V}, \ T_{MIN} \le T_A \le T_{MAX} \ \text{unless otherwise noted (Note 2) (} \ (T_A = T_J)$

| Symbol                   | Parameter                          | Test Conditions                                     |                                                                | LH0032 |       |                 | LH0032C |     |                | Units          |

|--------------------------|------------------------------------|-----------------------------------------------------|----------------------------------------------------------------|--------|-------|-----------------|---------|-----|----------------|----------------|

| Symbol                   |                                    |                                                     |                                                                | Min    | Тур   | Max             | Min     | Тур | Max            | - Office       |

| V <sub>OS</sub>          | Input Offset<br>Voltage            |                                                     | T <sub>A</sub> =T <sub>J</sub> =25°C<br>(Note 3)               |        | 2     | 5<br>10         |         | 2   | 15<br>20       | mV             |

| ΔV <sub>OS</sub> /<br>ΔT | Average Offset<br>Voltage Drift    |                                                     | (Note 4)                                                       |        | 15    | 50              |         | 15  | 50             | μV/°C          |

| I <sub>OS</sub>          | Input Offset<br>Current            | V <sub>IN</sub> =0                                  | T <sub>J</sub> =25°C (Note 3)<br>T <sub>A</sub> =25°C (Note 5) |        |       | 25<br>250<br>25 |         |     | 50<br>500<br>5 | pA<br>pA<br>nA |

| I <sub>B</sub>           | Input Bias<br>Current              |                                                     | T <sub>J</sub> =25°C (Note 3)<br>T <sub>A</sub> =25°C (Note 5) |        |       | 100<br>1<br>50  |         |     | 500<br>5<br>15 | pA<br>nA<br>nA |

| *V <sub>INCM</sub>       | Input Voltage<br>Range             |                                                     |                                                                | ±10    | ±12   |                 | ±10     | ±12 |                | V              |

| CMRR                     | Common Mode<br>Rejection<br>Ratio  | $\Delta V_{IN} = \pm 10V$                           |                                                                | 50     | 60    |                 | 50      | 60  |                | dB             |

| A <sub>VOL</sub>         | Open-Loop<br>Voltage               | $V_O = \pm 10V$ ,<br>f=1 kHz                        | T <sub>J</sub> =25°C                                           | 60     | 70    |                 | 60      | 70  |                | dB             |

|                          | Gain                               | $R_L = 1 k\Omega$ (Note 6)                          |                                                                | 57     |       |                 | 57      |     |                |                |

| V <sub>O</sub>           | Output Voltage<br>Swing            | $R_L = 1 k\Omega$                                   |                                                                | ±10    | ±13.5 |                 | ±10     | ±13 |                | V              |

| Is                       | Power Supply<br>Current            | T <sub>A</sub> =25°C,<br>I <sub>O</sub> =0 (Note 5) |                                                                |        | 18    | 20              |         | 20  | 22             | mA             |

| PSRR                     | Power Supply<br>Rejection<br>Ratio | $\Delta V_S = 10V$<br>(±5 to ±15V)                  |                                                                | 50     | 60    |                 | 50      | 60  |                | dB             |

<sup>\*</sup>Guaranteed by CMRR test condition.

#### AC Electrical Characteristics $V_S = \pm 15V$ , $R_L = 1k\Omega$ , $T_J = 25^{\circ}C$ (Note 7)

| Symbol         | Parameter                            | Con                              | Min                   | Тур | Max | Units |      |

|----------------|--------------------------------------|----------------------------------|-----------------------|-----|-----|-------|------|

| S <sub>R</sub> | Slew Rate                            | $A_V = +1$                       |                       | 350 | 500 |       | V/µs |

| ts             | Settling Time to 1% of Final Value   | $A_{V} = -1,$                    | $\Delta V_{IN} = 20V$ |     | 100 |       | ns   |

| t <sub>s</sub> | Settling Time to 0.1% of Final Value | ] /\v ',                         | 7 A IIV 50 A          |     | 300 |       | ns   |

| t <sub>R</sub> | Small Signal Rise Time               | $A_{V} = +1, \Delta V_{IN} = 1V$ |                       |     | 8   | 20    |      |

| t <sub>D</sub> | Small Signal Delay Time              |                                  |                       |     | 10  | 25    |      |

Note 1: In order to limit maximum junction temperature to  $\pm 175^{\circ}$ C, it may be necessary to operate with VS  $< \pm 15$ V when T<sub>A</sub> or T<sub>C</sub> exceeds specific values depending on the P<sub>D</sub> within the device package. Total P<sub>D</sub> is the sum of quiescent and load-related dissipation. See applications notes AN-277, "Applications of Wide-Band Buffer Amplifiers" and AN-253, "High-Speed Operational-Amplifier Applications" for a discussion of load-related power dissipation.

Note 2: LH0032G is 100% production tested as specified at 25°C, 125°C, and -55°C. LH0032CG is 100% production tested at 25°C only. Specifications at temperature extremes are verified by sample testing, but these limits are not used to calculate outgoing quality level.

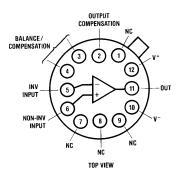

Note 3: Specification is at 25°C junction temperature due to requirements of high-speed automatic testing. Actual values at operating temperature will exceed the value at  $T_J = 25$  C. When supply voltages are  $\pm$  15V, no-load operating junction temperature may rise 40–60°C above ambient, and more under load conditions. Accordingly,  $V_{OS}$  may change one to several mV, and  $I_B$  and  $I_{OS}$  will change significantly during warm-up. Refer to  $I_B$  and  $I_{OS}$  vs. temperature graph for expected values.

Note 4: LH0032G is 100% production tested for this parameter. LH0032CG is sample tested only. Limits are not used to calculate outgoing quality levels.  $\Delta V_{OS}/\Delta T$  is the average value calculated from measurements at 25°C and  $T_{MAX}$ .

Note 5: Measured in still air 7 minutes after application of power. Guaranteed thru correlated automatic pulse testing.

Note 6: Guaranteed thru correlated automatic pulse testing at  $T_J = 25^{\circ}C$ .

Note 7: Not 100% production tested; verified by sample testing only. Limits are not used to calculate outgoing quality level.

Note 8: For operating at elevated temperatures, the device must be derated based on the thermal resistance  $\theta_{JA}$  and  $T_J$  max.  $T_J = T_A + P_D\theta_{JA}$ .

Note 9: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed.

Note 10: The maximum power dissipation is a function of maximum junction temperature  $T_J$  max, total thermal resistance  $\theta_{JA}$ , and ambient temperature  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_J \max_J - T_A)/\theta_{JA}$ .

Note 11: See RETS0032X for LH0032G military specifications.

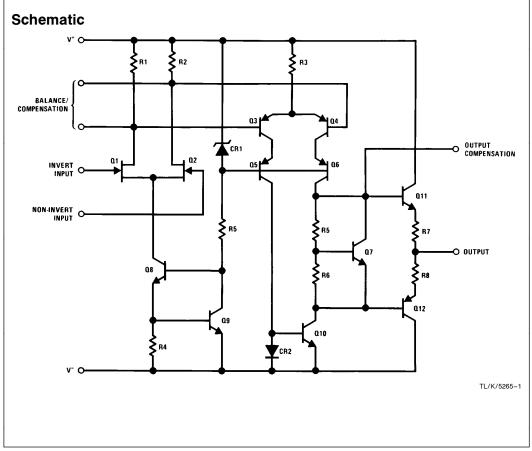

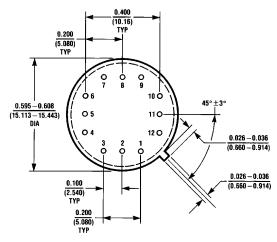

#### **Connection Diagram**

TL/K/5265-23

Order Number LH0032G, LH0032G/883 or LH0032CG See NS Package Number G12B

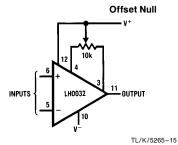

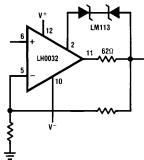

## **Auxiliary Circuits**

## **Output Short Circuit Protection**

TL/K/5265-16

## **Typical Applications**

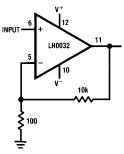

**Unity Gain Amplifier**

TL/K/5265-17

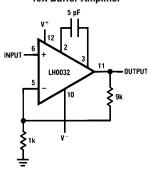

10X Buffer Amplifier

TL/K/5265-18

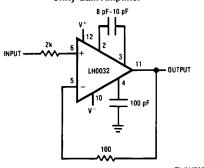

#### 100X Buffer Amplifier

TL/K/5265-19

#### Non-Compensated Unity Gain Inverter

TL/K/5265-20

### **Typical Applications** (Continued)

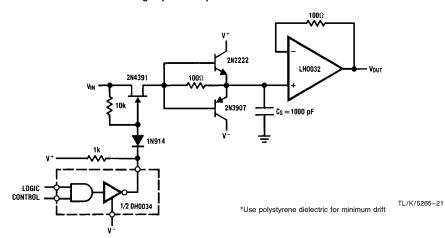

#### High Speed Sample and Hold

### **Applications Information**

#### POWER SUPPLY DECOUPLING

The LH0032/LH0032A, like most high speed circuits, is sensitive to layout and stray capacitance. Power supplies should be by passed as near to pins 10 and 12 as practicable with low inductance capacitors such as 0.01  $\mu F$  disc ceramics. Compensation components should also be located close to the appropriate pins to minimize stray reactances.

#### INPUT CURRENT

Because the input devices are FETs, the input bias current may be expected to double for each 11°C junction temperature rise. This characteristic is plotted in the typical performance characteristics graphs. The device will self-heat due to internal power dissipation after application of power thus raising the FET junction temperature  $40-60^{\circ}\text{C}$  above free-air ambient temperature when supplies are  $\pm$  15V. The de-

#### **Applications Information** (Continued)

vice temperature will stabilize within 5–10 minutes after application of power, and the input bias currents measured at that time will be indicative of normal operating currents. An additional rise would occur as power is delivered to a load due to additional internal power dissipation.

There is an additional effect on input bias current as the input voltage is changed. The effect, common to all FETs, is an avalanche-like increase in gate current as the FET gate-to-drain voltage is increased above a critical value depending on FET geometry and doping levels. This effect will be noted as the input voltage of the LH0032 is taken below ground potential when the supplies are  $\pm\,15V.$  All of the effects described here may be minimized by operating the device with  $V_S\!\le\!\pm\,15V.$

These effects are indicated in the typical performance curves.

#### **INPUT CAPACITANCE**

The input capacitance to the LH0032/LH0032C is typically 5pF and thus may form a significant time constant with high value resistors. For optimum performance, the input capacitance to the inverting input should be compensated by a small capacitor across the feedback resistor. The value is strongly dependent on layout and closed loop gain, but will typically be in the neighborhood of several picofarads.

In the non-inverting configuration, it may be advantageous to bootstrap the case and/or a guard conductor to the inverting input. This serves both to divert leakage currents away from the non-inverting input and to reduce the effective input capacitance. A unity gain follower so treated will have an input capacitance under a picofarad.

#### HEAT SINKING

While the LH0032/LH0032A is specified for operation without any explicit heat sink, internal power dissipation does cause a significant temperature rise. Improved bias current performance can thus be obtained by limiting this temperature rise with a small heat sink such as the Thermalloy No. 2241 or equivalent. The case of the device has no internal connection, so it may be electrically connected to the sink if this is advantageous. Be aware, however, that this will affect the stray capacitances to all pins and may thus require adjustment of circuit compensation values.

For additional applications information request Application Note AN-253.

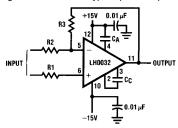

#### Compensating the LH0032

With the LH0032, two compensation schemes may be used, depending on the designer's specific needs.

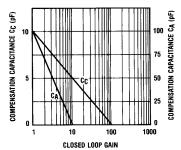

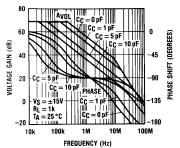

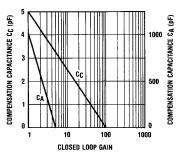

The first technique is shown in Figure 14. It offers the best 0.1% settling time for a  $\pm\,10V$  square wave input. The compensation capacitors  $C_C$  and  $C_A$  should be selected from Figure 15 for various closed-loop gains. Figure 16 shows how the LH0032 frequency response is modified for different value compensation capacitors.

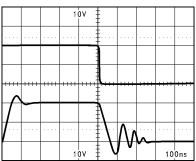

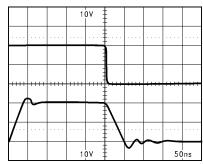

Although this approach offers the shortest settling time, the falling edge exhibits overshoot up to 30% lasting 200 to 300 ns. *Figure 17* shows the typical pulse response.

TL/K/5265-27

FIGURE 14. LH0032 Frequency Compensation Circuit

TL/K/5265-28

FIGURE 15. Recommended Value of Compensation Capacitor vs. Closed-Loop Gain for Optimum Settling Time

#### **Applications Information (Continued)**

TI /K/5265-29

FIGURE 16. The Effect of Various Compensation Capacitors on LH0032 Open Loop Frequency Response

TI /// EDGE 20

FIGURE 17. LH0032 Unity Gain Non-Inverting Large Signal Pulse Response:  $T_A = 25^{\circ}C, C_C = 10 \ pF, C_A = 100 \ pF$

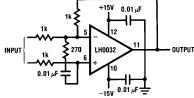

If obtaining minimum ringing at the falling edge is the primary objective, a slight modification to the above is recommended. It is based on the same circuit as that of *Figure 14*.

The values of the unity gain compensation capacitors CC and CA should be modified to 5 pF and 1000 pF, respectively. Figure 18 shows the suitable capacitance to use for various closed-loop gains. The resulting unity gain pulse response waveform is shown in Figure 19. The settling time to 1% final value is actually superior to the first method of compensation. However, the LH0032 suffers slow settling thereafter to 0.1% accuracy at the falling edge, and nearly four times as much at the rising edge, compared to the previous scheme. Note, however, that the falling edge ringing is considerably reduced. Furthermore, the slew rate is consistently superior using this compensation because of the smaller value of Miller capacitance C<sub>C</sub> required. Typical improvement is as much as 50%. A more detailed discussion of this effect is provided in the Slew Response section of this Application Note.

The second compensation scheme works well with both inverting or non-inverting modes. Figure 20 shows the circuit

TI /K/5265\_3

FIGURE 18. Recommended Value of Compensation Capacitor vs. Closed-Loop Gain for Optimum Slew Rate

TL/K/5265-32

FIGURE 19. LH0032 Unity Gain Non-Inverting Large Signal Pulse Response:  $C_C = 5 \ \text{pF}, \ C_A = 1000 \ \text{pF}$

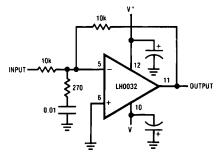

schematic, in which a 270 $\Omega$  resistor and a 0.01  $\mu F$  capacitor are shunted across the inputs of the device. This lag compensation introduces a zero in the loop modifying the response such that adequate phase margin is preserved at unity gain crossover frequency. Note that the circuit requires no additional compensation.

TL/K/5265-33

FIGURE 20. LH0032 Non-Compensated Unity Gain Compensation

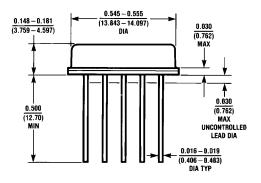

### Physical Dimensions inches (millimeters)

G12B (REV C)

Metal Can Package (G)

Order Number LH0032G, LH0032G/883 or LH0032CG

NS Package Number G12B

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Europe

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 180-530 85 85

English Tel: +49 (0) 180-532 78 82

Français Tel: +49 (0) 180-532 93 58

Italiano Tel: +49 (0) 180-542 416 80

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2308 Fax: 81-043-299-2408