# **Application Note AN-51 HiperTFS**<sup>™</sup> Family

**Design Considerations**

# Introduction

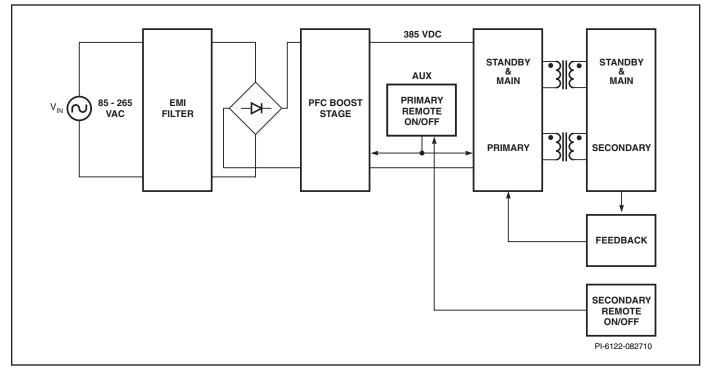

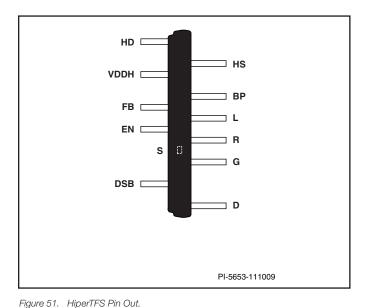

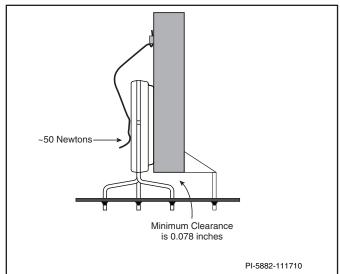

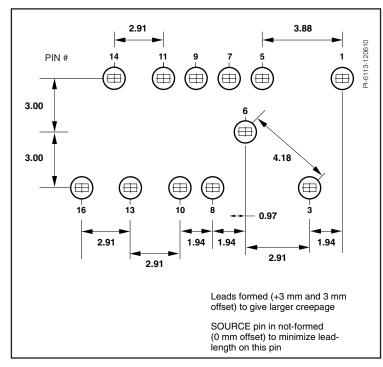

The HiperTFS is highly integrated, very efficient integrated offline switcher IC mainly intended for PC main and standby applications. The IC includes the control, drivers and switches for a two-switch forward high power main converter and the control and power switch for a flyback standby converter. A minimal count of external components are required for full operation. The HiperTFS package (eSIP-16B) requires no electrical isolation of the exposed back tab, enabling direct mounting to a heat sink for maximally effective heat sinking and minimal mounting hardware. The HiperTFS series covers a range from 170 W to 415 W continuous power output (at 25 °C ambient) and in applications such as PC power supplies which require very dense and compact layout and high efficiency. HiperTFS provides significant advantages to the designer whether it be for 70 PLUS, 80 PLUS or 80 PLUS Bronze compliant designs.

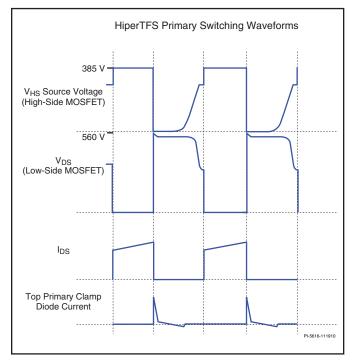

The main forward converter is intended to work with a PFC boost front end provides a regulated voltage from 290 VDC to 420 VDC input (385 VDC typical). The standby section of HiperTFS is intended for wide range operation from 100 VDC to 420 VDC. High efficiency is made possible by using an asymmetrical version of the two-switch forward which allows an operating duty cycle greater than 50%, hence lower RMS switch currents and lower output diode voltage ratings. A proprietary protection circuit guarantees safe operation by limiting the forward transformer single cycle flux and guaranteeing transformer reset, eliminating transformer saturation under all conditions. Special functions include OVP latch for standby, remote-ON/OFF capability for the main converter, programmable maximum primary current limit ranges for main and standby supplies, frequency jitter for low EMI, and flat standby output overload characteristics with respect to input voltage.

# **Basic Circuit Configuration**

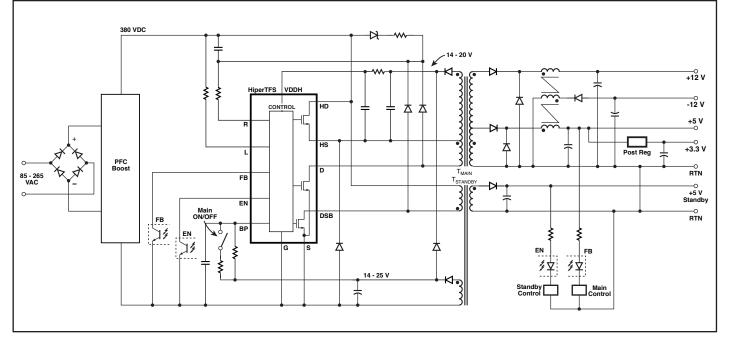

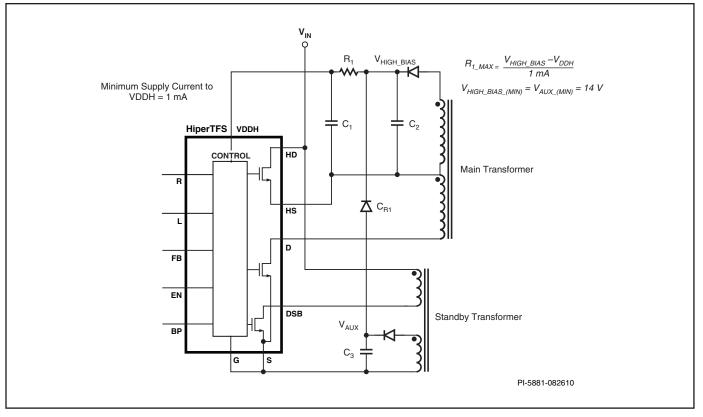

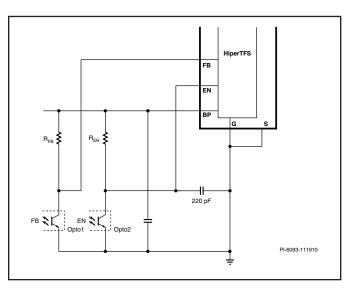

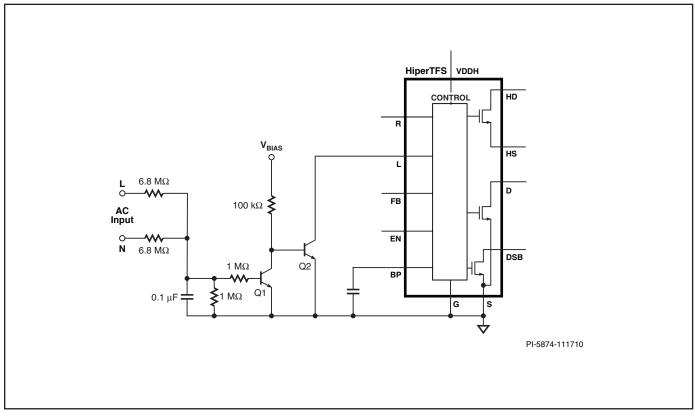

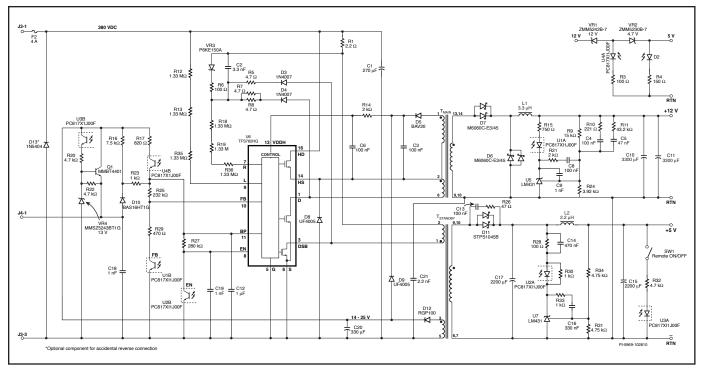

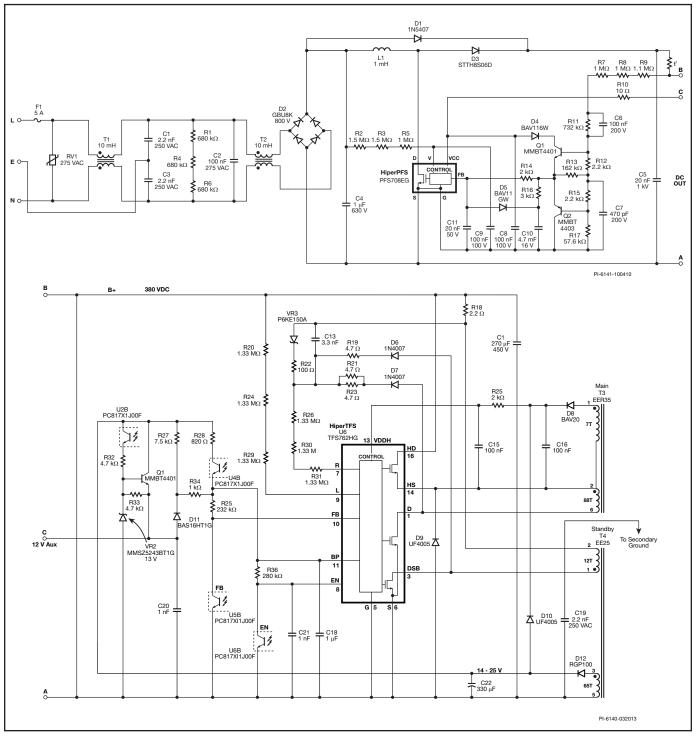

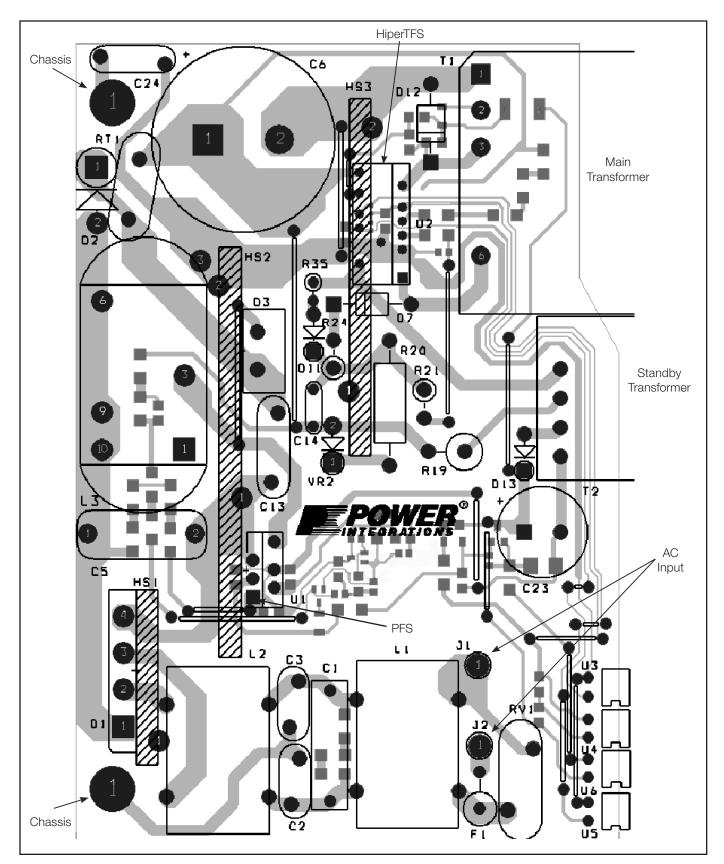

The circuit shown in Figure 1 shows the basic configuration of a PC power supply design using HiperTFS, including main and standby converters. The high level of integration of HiperTFS, provides many of the needed functions that would otherwise require external circuitry saving development time and material costs. One common external circuit configuration is useful for a range of applications. Advanced features like line undervoltage and overvoltage protection, reset and flux density limiter for main transformer, external current limit selection, start-up features, and remote-ON/OFF are easily implemented with a minimal number of external components.

Other application specific issues such as constant current, and constant power outputs, etc. are beyond the scope of this design guide. However, if required such specifications may be satisfied by adding additional circuitry to the basic converter configuration.

Figure 1. A Simplified Schematic of HiperTFS With PC Main Supply With 3.3 V, 5 V, 12 V, -12 V and One +5 V Standby Output.

# Scope

This application note is intended for engineers designing an isolated AC-DC forward power supply with flyback standby using the HiperTFS family of devices. It is assume that there is a power factor converter boost stage (HiperPFS) providing 385 VDC to the input of the main converter. The standby converter must operate with the PFC boost stage both on or off so the standby has a wide DC operating input range of 100 VDC to 420 VDC. For detailed information on PFC stage refer to HiperPFS application note. Guidelines and a step-by-step walk through of the HiperTFS design spreadsheet are given to enable an engineer to quickly select key components and design a suitable main transformer, standby transformer and main output inductor design for a PC power supply. This application note refers directly to the PIXIs design spreadsheet that is part of the PI Expert<sup>™</sup> design software suite. The basic configuration used in PC power supply is shown in Figure 1, which also serves as the reference circuit for component identifications used in the description throughout this application note.

In addition to this application note the reader may also find the HiperTFS Reference Design Kit (RDK-249) containing an engineering prototype board, engineering report and device samples useful as an example of a working power supply. There is also an engineering report available describing a full multiple output design for PC main applications. Further details on downloading PI Expert, obtaining a RDK and updates to this document can be found at www.powerint.com.

# **Overview of Design Method**

Readers needing to start immediately can use the following information to quickly design the transformer and select the components for a first prototype. The information described below needs to be entered into the PIXIs design spreadsheet. Other parameters will be automatically selected based on a typical design. References to spreadsheet cell locations are provided in square brackets [cell reference].

# **Design Using PIXIs**

#### **Description of PIXIs Format**

There are four major sections in this spreadsheet:

- 1. Input parameters and device selection and device configuration.

- 2. Transformer core selection and winding design for main forward converter.

- 3. Output coupled inductor core size and core material selection and winding design for main forward.

- 4. Standby transformer design.

Each of these sections have grayed cells that are locations for user enterable parameters. When PIXIs is first opened these grayed cells will contain default values already entered for a typical 300 W output main 17 W output standby design. The designer is advised to leave these cells unchanged unless they have more precise information.

# **Output Voltages and Currents of Main Converter**

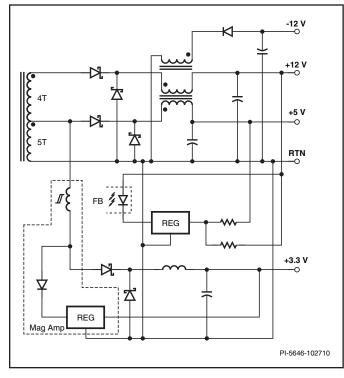

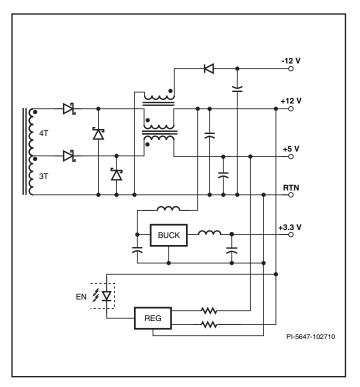

There are commonly four output voltages provided by a PC main converter. These are +5 V, +12 V, +3.3 V and -12 V. The main transformer usually has only two output windings which source the +5 V and +12 V outputs. The outputs of these two windings are rectified and drive the input of a coupled main output inductor. The third output, commonly a 3.3 V output, is derived from a switching post regulator, which is typically a mag amp sourced from the +5 V winding or a synchronous buck converter sourced from the +12 V output. Finally, there is commonly a -12 V output sourced from a flyback winding on the coupled output inductor (intended for light loads only).

## Section 1 – Input Parameters, Device Selection and Device Configuration

## Step 1 – Enter Output Current and Voltages \*note

brackets[] indicate actual spreadsheet name parentheses() indicates typical value

- Enter output current and voltage values for  $[V_{_{MAIN}}]$  and  $[I_{_{MAIN}}]$  (+12 V).

\*note -  $V_{MAIN}$  is highest power output.

- Enter output current and voltage values for  $[V_{_{OUT2}}]$  and  $[I_{_{OUT2}}]$  (+5 V).

- Enter output current and voltage values for post regulator  $\rm [V_{outs}]$  and  $\rm [I_{outs}]$  (+3.3 V).

- Select type of post regulation[Post Regulator] (MAG AMP, Buck or NONE).

- If buck post regulator is selected enter estimated efficiency of buck stage [n\_PR]. This is ignored if MAG AMP was chosen.

- Enter voltage and current of inductor derived output (-12 V),  $[\rm V_{OUT4}]$  and  $[\rm I_{OUT4}].$

- [P<sub>OUT(MAIN</sub>] is the total maximum output power of the main converter which is the sum of the output power of all main converter outputs.

- If there is a peak power requirement then enter the peak power in [P<sub>OUT\_PEAK(MAIN</sub>]. The additional power over continuous maximum output power is assumed to be sourced from V<sub>MAIN</sub>.

- [P<sub>OUT(STANDBY)</sub>] and [P<sub>OUT\_PEAK(STANDBY)</sub>] have default values entered These will later change when entering actual standby output power in standby section of spreadsheet.

- $[V_{\text{BIAS}}]$  is typically 17 V which is used for bias support of HiperTFS bootstrap high-side drive, and the source for the +12 V regulator which is used for remote, ON/OFF and bias for HiperPFS boost controller. Changing the target voltage of V\_{BIAS} could be detrimental to supply performance.

| HiperTFS MAIN OUTPUT (TWO-SWITCH FORWARD S  | TAGE)   |           |   |                                                                                |

|---------------------------------------------|---------|-----------|---|--------------------------------------------------------------------------------|

| OUTPUT VOLTAGE AND CURRENT                  |         |           |   | Design Title                                                                   |

| VMAIN                                       | 12.00   |           | V | Main output voltage                                                            |

| IMAIN                                       | 15.00   |           | A | Main output current                                                            |

| VOUT2                                       | 5.00    |           | V | Output2 voltage                                                                |

| IOUT2                                       | 15.00   |           | A | Output2 current                                                                |

| POST REGULATED OUTPUT                       |         | <br>      |   |                                                                                |

| Post Regulator                              | MAG-AMP |           |   | Select post regulator from Mag-Amp or Buck                                     |

| V_SOURCE                                    | 5.00    |           | V | Select source of input voltage for post regulator                              |

| VOUT3                                       | 3.30    | 3.3       | V | Enter postregulator output voltage                                             |

| IOUT3                                       | 10.00   | 10.0      | A | Enter post rehulator output current                                            |

| n_PR                                        |         | 1         |   | Enter postregulator efficiency (Buck only)                                     |

| COUPLED-INDUCTOR (LOW POWER) DERIVED OUTPUT |         | <br>      |   |                                                                                |

| VOUT4                                       | 12.00   |           | V | Coupled-Inductor derived (low power) output voltage (typically -12 V)          |

| IOUT4                                       | 0.10    |           | A | Coupled-Inductor derived (low power) output current                            |

| POUT(Main)                                  |         | <br>289.2 | w | Total output power (Main converter)                                            |

|                                             |         |           |   | Peak Output power(Main converter). If there is no peak power requirement enter |

| POUT_PEAK(Main)                             |         | 289.2     | W | value equal to continuous power                                                |

| POUT(Standby)                               |         | 10.3      | W | Continuous output power from Standby power supply                              |

| POUT_PEAK(Standby)                          |         | 17.5      | W | Peak output power from Standby section                                         |

| POUT(System Total)                          |         | 299.5     | w | Total system continuous output power                                           |

| POUT_PEAK(System Total)                     |         | 306.7     | W | Total system peak output power                                                 |

| VBIAS                                       | 17.00   |           | V | DC bias voltage from main transformer aux winding                              |

Figure 2. Main Converter Design Parameters.

Figure 3. Typical Output Configurations for Post Regulator. Mag Amp Regulated.

Figure 3a. Typical Output Configurations for Post Regulator. Buck Regulated.

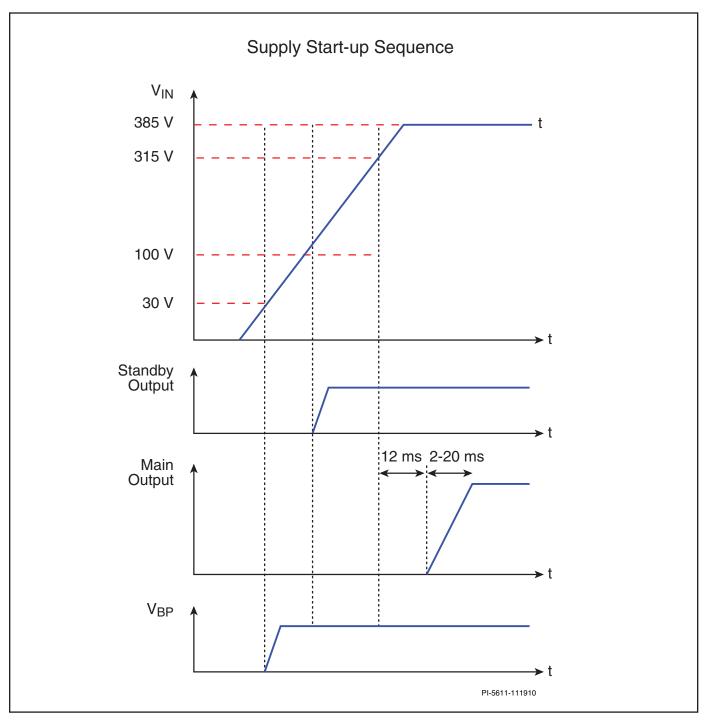

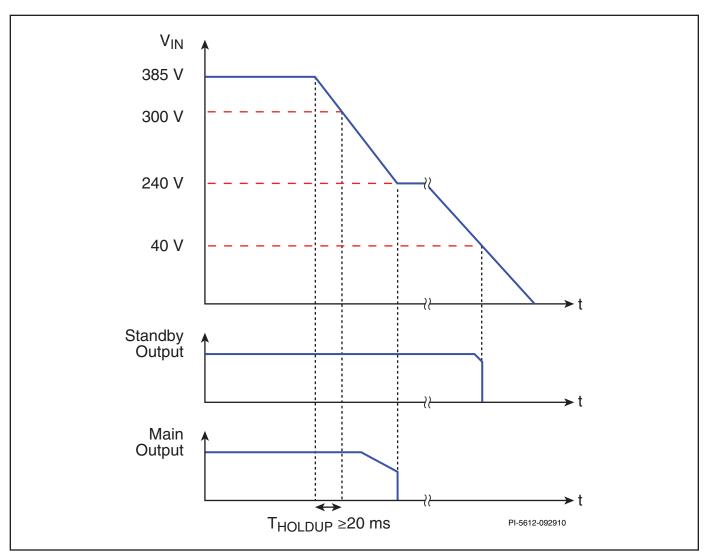

#### Undervoltage Lockout and Hold-Up Time

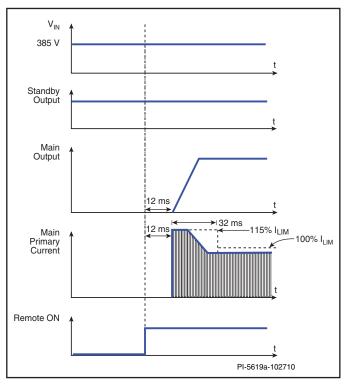

The DC input voltage to the converter is sensed by the LINE-SENSE (L) pin which receives current from the line sense resistor. The line sense resistor is typically 4 M $\Omega$  and the chart below shows the UV threshold for the Standby and Main converters with this value. Also note that there is a fixed 12 ms delay between the time [V<sub>OV(ON)</sub>] is reached for the main converter and the actual start of main converter switching (this gives time for the PFC output voltage to settle).

Critical inputs for determining hold-up time  $[T_{\text{HOLDUP}}]$  are the nominal operating voltage  $[V_{\text{NOM}}]$  and the minimum input voltage  $[V_{\text{MIN}}]$  that guarantees regulation at maximum specified continuous output power. By specifying a holdup time at a given output power and knowing  $V_{\text{NOM}}$  and  $V_{\text{MIN}}$ , the input minimum output capacitor can be computed.

$$C_{MIN} = \frac{2 \times P_{OUT\_TOTAL} \times T_{HOLDUP}}{0.86 \times ((V_{NOM})^2 - (V_{MIN})^2)}$$

Figure 4. Power Supply Start-Up Sequence (Voltages Shown Assume a 4 MΩ Line Sense Resistor).

Figure 5. Power Supply Shutdown Sequence (AC Turn-Off).

#### Step 2 - Hold-Up Time and Input Voltage Range

Below are the steps for defining hold-up time and input voltage range.

- Enter desired minimum holdup time [T<sub>HOLDUP</sub>] at maximum

- continuous output power [P\_{OUT(SYSTEM TOTAL]}]. Enter minimum [V\_{MIN}] and nominal [V\_{NOM}] input voltages to define regulation range for the forward converter.  $[V_{NOM}]$  is the nominal output voltage from the PFC boost stage DC bus.

- · After these values are entered view [CIN] to see the minimum required input capacitance. If nothing is entered for  $[V_{\text{MIN}}]$ ,  $[V_{NOM}]$  and  $[T_{HOLDUP}]$  the spreadsheet will show default values  $[V_{MIN}] = 300, [V_{NOM}] = 385$ , and  $[T_{HOLDUP}] = 20$  ms. If desired holdup time is different than the default value, then enter required holdup time  $[\mathrm{T}_{\mathrm{HOLDUP}}]$  and check required  $[\mathrm{C}_{\mathrm{IN}}].-$

- Enter maximum input voltage  $[V_{MAX}]$ . This is used to determine maximum voltage stress on switching components.

- R<sub>B</sub> and R<sub>1</sub> are computed resistor values for L an R pin functions which include  $[V_{UV(ON)}]$  and  $[V_{UV(OFF)}]$ . The default values are 4 M $\Omega$ . These values normally do not need adjusting.

- $[V_{IM(ON)}]$  is the start-up threshold for the main converter and  $[V_{\mbox{\tiny UV(OFF)}}]$  is the shut down threshold for the main converter.

- The values of  ${\sf R}_{_{\sf R}}$  and  ${\sf R}_{_{\sf I}}$  are nominally 4  $M\Omega$  unless an override value is entered for R<sub>1</sub>. Entering a different value for  $R_{_{I}}$  which will create a new identical value for  $R_{_{R}}$ . Lowering  $R_{_{I}}$ and  $\rm R_{_R}$  value will lower both  $\rm V_{_{UV(ON)}}$  and  $\rm V_{_{UV(OFF)}}$  threshold, but will also reduce maximum operating duty cycle [DMAX<sub>VNOM</sub>] and [DMAX<sub>VMIN</sub>]. A value that is too low will usually cause the spreadsheet to flag inadequate hold-up time. A value higher than 4 M $\Omega$  is not advised as this may cause the spreadsheet to flag core reset problems [BP<sub>MAX</sub>].

| INPUT VOLTAGE AND UV/OV |   |      |        |       |                                                                             |

|-------------------------|---|------|--------|-------|-----------------------------------------------------------------------------|

| CIN                     |   |      | 262.23 | uF    | Input Capacitance. To increase CMIN, increase T_HOLDUP                      |

| T_HOLDUP                |   |      | 20.00  | ms    | Holdup time                                                                 |

| VMIN                    |   |      | 300    | V     | Minimum input voltage to guarantee output regulation                        |

| VNOM                    |   |      | 380    | V     | Nominal input voltage                                                       |

| VMAX                    |   |      | 420    | V     | Maximum DC input voltage                                                    |

| UV / OV / UVOV          |   | min  | max    |       |                                                                             |

| VUV OFF                 | 2 | 36.0 | 287.9  | V     | Minimum undervoltage On-Off threshold                                       |

| VUV ON                  | 3 | 00.0 | 344.7  | V     | Maximum undervoltage Off-On threshold (turn-on)                             |

| VOV ON                  | 4 | 80.4 | -      | V     | Minimum overvoltage Off-On threshold                                        |

| VOV OFF                 | 6 | 64.5 | -      | V     | Minimum overvoltage On-Off threshold (turn-off)                             |

| RR                      |   |      | 4.03   | M-ohm | R pin resistor                                                              |

|                         |   |      |        |       | Line Sense resistor value (L-pin) - goal seek (VUV OFF) for std 1% resistor |

| RL                      |   |      | 4.03   | M-ohm | series                                                                      |

Figure 6. Power Supply Under/Overvoltage and Input Capacitor Parameters.

#### Step 3 – Selecting HiperTFS Device, Current Limit Setting and KDI Goal and Clamp Selection

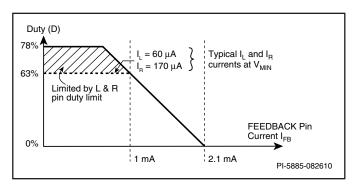

There are several HiperTFS devices available in the family. The appropriate device depends on the output power, type of application and thermal environment. For example in PC power supplies two different ambient requirements are commonly used. Original equipment manufacturer (OEM) power output is specified at 50 °C ambient where as clones typically are specified at 25 °C ambient. Table 1 shows which device is best suited for a given ambient temperature. There is also the option to select one of three current limit values. Selection is made by entering a value for KI [KI] of either 1, 0.8 or 0.6. These values correspond to the data sheet parameters  $I_{\text{LIM}(3)\text{MA}},~I_{\text{LIM}(2)\text{MA}}$  and  $I_{\text{LIM}(1)\text{MA}}$ respectively. The resultant minimum device current limit is shown in cell  $[I_{\text{LIMITSELECT}}]$ . Implementing the selected KI is achieved by selecting the value of pull-up resistor from the FEEDBACK to the BYPASS pin of the HiperTFS device.  $[R_{EB}]$ shows the appropriate value for the pull-up resistor for the selected KI. Table 2 shows the relationship between  $I_{_{\rm FB}}$  and selected current limit.

#### Р<sub>оит</sub> Т<sub>4</sub> = 50 °С P<sub>out</sub> PK P<sub>OUT</sub> Р<sub>оит</sub> Т<sub>4</sub> = 25 °С Part Number Standby TFS757HG 193 W 163 W 228 W 20 W TFS758HG 236 W 200 W 278 W 20 W TFS759HG 309 W 280 W 235 W 20 W TFS760HG 305 W 258 W 358 W 20 W TFS761HG 326 W 276 W 383 W 20 W TFS762HG 360 W 304 W 407 W 20 W TFS763HG 388 W 327 W 455 W 20 W TFS764HG 414 W 344 W 530 W 20 W

Output Power Table

Table 1. HiperTFS Output Power Table.

| I <sub>FB</sub><br>(Threshold) | Datasheet<br>Parameters | Percent of<br>I <sub>LIM(3)MA</sub> | $R_{FB}$ | R <sub>FB</sub> (1%) |  |

|--------------------------------|-------------------------|-------------------------------------|----------|----------------------|--|

| 0.0-5.1 μΑ                     | LIM(1)MA                | 60                                  | Open     |                      |  |

| 5.1-11.9 μA                    | I <sub>LIM(2)MA</sub>   | 80                                  | 511.0    | kΩ                   |  |

| 11.9-23.8 μA                   | I <sub>LIM(3)MA</sub>   | 100                                 | 232.0    | kΩ                   |  |

Table 2. FEEDBACK Pin Main Current Limit Selection.

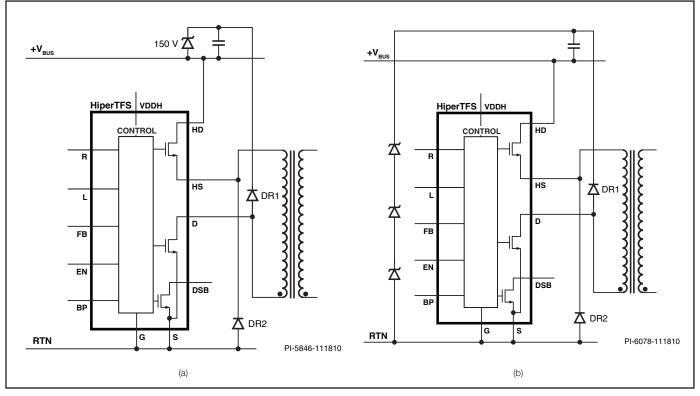

For a two-switch Forward topology, power is delivered during the on-time of the main switches. During the off-time, both leakage and magnetizing energy in the main transformer must be reset and recovered in a safe manner. There are two options for main transformer reset within [CLAMP SELECTION]: clamp-to-rail and clamp-to-ground (see Figure 7 for both clamp schematics). Clamp-to-rail clamps the bottom main switch to a constant value above the input DC bus (385 VDC). This is the simplest and least expensive clamp method and also has the convenience of allowing the standby converter to share the clamp network. Clamp-to-ground is the second option which creates a constant reset voltage with respect to primary ground and has the advantage of allowing wider nominal operating duty cycle, which offers either the advantage of lower RMS current for the primary main switches of HiperTFS or allows the use of a smaller input bulk capacitor. The default nominal duty cycle  $[D_{VNOM}]$  for clamp-to-rail is 0.45 and the default for clamp-to-ground is 0.49.

#### Step 4 – Spreadsheet Procedure for Device Selection and Configuration

- Review the output power table and decide appropriate HiperTFS device depending on application, ambient temperature and output power.

- Select HiperTFS device [DEVICE] from drop down list.

- Selected HiperTFS device and key device parameters are displayed [Line 42-48].

- Select primary current limit factor [KI]. 1, 0.8, 0.6. [I<sub>LIMIT</sub>] default value is 1.

- The default nominal operating duty cycle is 45% for clamp-torail. Notice from Figure 7 the circuit includes a 150 V Zener. This allows a maximum duty cycle at V<sub>MIN</sub> to be greater than 58% for the example spreadsheet shown. [D<sub>MAX</sub> V<sub>MIN</sub>] is typically 60% for clamp-to-rail setting. The value of the clamp Zener is selectable; however, a value range from 130 V to 150 V is advised. Care should be taken when entering a duty cycle higher than 45% for clamp-to-rail as it may cause a T<sub>HOLDUP</sub> warning. Generally higher nominal operating duty cycles require changing the clamp mode to clamp-to-ground to increase reset voltage across transformer during brownout. A nominal operating duty cycle of up to 50% can be achieved with clamp-to-ground. The default value of [V<sub>CLAMP</sub>] in clamp-to-ground configuration is 530 V.

Another option to allow higher operating duty cycle is to raise  $V_{\text{MIN}}$  for the same holdup time and use a higher  $C_{\text{IN}}$  value. Note that in both configurations of clamp circuit DR1 is a slow recovery diode (1N4007G) which allows recycling of the magnetizing and leakage energy. A 1N4007G which is glass passivated is preferred over 1N4007 because it has well controlled reverse recovery characteristics. Using a slow recovery diode rather than a fast recovery type increases overall

Figure 7. Clamp-to-Rail (a) and Clamp-to-Ground (b).

| ENTER DEVICE VARIABLES |               |        | 1      |                                                                                     |

|------------------------|---------------|--------|--------|-------------------------------------------------------------------------------------|

| Device                 | TFS762        |        |        | Selected HiperTFS device                                                            |

|                        | 11-3/62       | 750700 |        | Selected hiper h S device                                                           |

| Chosen Device          |               | TFS762 |        |                                                                                     |

| ILIMIT_MIN             |               | 3.26   | A      | Device current limit (Minimum)                                                      |

| ILIMIT_TYP             |               | 3.50   | A      | Device current limit (Typical)                                                      |

| ILIMIT_MAX             |               | 3.75   | A      | Device current limit (Maximum)                                                      |

| fSMIN                  |               | 61500  | Hz     | Device switching frequency (Minimum)                                                |

| fS                     |               | 66000  | Hz     | Device switching frequency (Typical)                                                |

| fSMAX                  |               | 70500  | Hz     | Device switching frequency (Maximum)                                                |

|                        |               |        |        |                                                                                     |

| KI                     | 1.0           | 1.0    |        | Select Current limit factor (KI=1.0 for default ILIMIT, or select KI=0.8 or KI=0.6) |

| R(FB)                  |               | 232.0  | k-ohms | Feedback Pin Resistor value                                                         |

| ILIMIT SELECT          |               | 3.26   | A      | Selected current limit                                                              |

| RDS(ON)                |               | 2.73   | ohms   | Rds(on) at 100'C                                                                    |

| DVNOM_GOAL             |               | 0.45   |        | Target duty cycle at nominal input voltage (VNOM)                                   |

| VDS                    |               | 4.80   | V      | HiperTFS average on-state Drain to Source Voltage                                   |

| Clamp Selection        | CLAMP TO RAIL |        |        | Select either "CLAMP TO RAIL" (default) or "CLAMP TO GND"                           |

| VCLAMP                 |               | 150.00 | V      | Asymmetric Clamp Voltage                                                            |

| VDSOP                  |               | 570.00 | V      | Maximum HiperTFS Drain voltage (at VOVOFF_MAX)                                      |

Figure 8. HiperTFS Main Current Limit, Device Selection and Other Design Parameters.

efficiency and reduces dissipation of clamp Zener (D3) by recycling energy clamp. The bottom catch diode DR2 is typically an ultra fast type rectifier (UF4005).

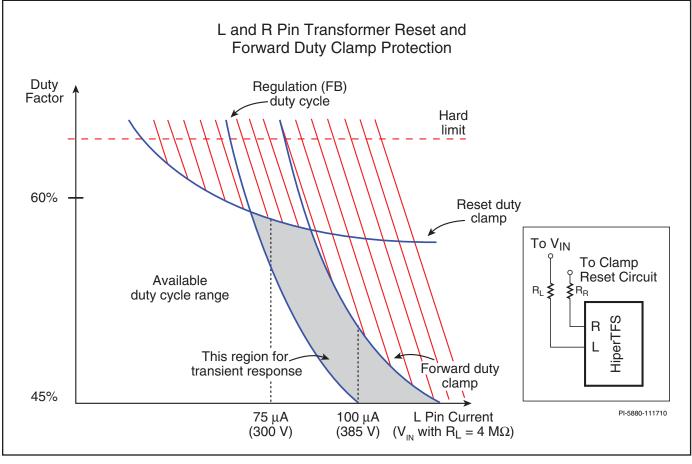

# Prevention of Core Saturation by LINE-SENSE and RESET Pin Maximum Duty Cycle Limit Function

By sensing the input voltage through the LINE-SENSE pin and the clamp voltage through the RESET pin, HiperTFS can determine the duty cycle boundary for safe operation and will limit the maximum duty below this level. Figure 9 shows the allowable duty cycle range as a function of  $V_{\rm IN}$ .

Saturation of the main transformer can commonly occur by one of two possible mechanisms:

1. Lack of sufficient reset volt-seconds for the core during the off-time.

2. Applying excessive volt-seconds to the core during the on-time cycle.

HiperTFS safely limits the duty cycle to avoid these two possible conditions.

The equations below determine the maximum duty cycle allowed by LINE-SENSE and RESET pin limiter for reset of core.

Clamp-to-Rail:

$$D_{\text{MAX}_{\text{FORWARD}(\text{VMIN})}} = \frac{V_{\text{CLAMP}} + (V_{\text{MIN}} - V_{\text{DS}})}{2(V_{\text{MIN}} - V_{\text{DS}}) + V_{\text{CLAMP}}}$$

Clamp-to-Ground:

$$D_{\text{MAX\_RESET(VMIN)}} = \frac{V_{\text{CLAMP}}}{(V_{\text{MIN}} - V_{\text{DS}}) + V_{\text{CLAMP}}}$$

Figure 9. Duty Cycle Limiter (Clamp-to-Rail using 150 V Zener Diode Network).

The equation below determines the maximum duty cycle allowable to avoid excessive peak flux density resulting from on-time volt-seconds.

$$D_{MAX(ON)} = \frac{5.2 \times 10^{-5} \times R_L}{V_{IN(MAX)}}$$

#### Step 5 - Output Diode Selection

Select appropriate diodes for the various outputs. Figure 10 shows typical forward voltage drops used for diodes +5 V, +12 V, +3.3 V, and standby. Depending on output current and data sheet values for diode forward voltage drop, the section below allows the designer to enter expected voltage drop

across output diode at maximum continuous output current for that output. These values will effect computed nominal duty cycle and turns ratio of main transformer.

• The default values for output diodes are 0.5 V for Schottky and 0.7 V for PN junction type. For a lower forward drop Schottky enter appropriate value [B62-B65].

Keep in mind that the wide operating duty cycle of HiperTFS results in a lower peak output diode reverse voltage for the output catch diode . Choose diodes with lower reverse voltage to take advantage of lower  $\rm V_{\rm F}$  (and lower dissipation) where possible.

| DIODE Vf SELECTION |  |     |   |                                              |

|--------------------|--|-----|---|----------------------------------------------|

| VDMAIN             |  | 0.5 | V | Main output diodes forward voltage drop      |

| VDOUT2             |  | 0.5 | V | Secondary output diodes forward voltage drop |

| VDOUT3             |  | 0.5 | V | 3rd output diodes forward voltage drop       |

| VDB                |  | 0.7 | V | Bias diode forward voltage drop              |

Figure 10. Output Diode Forward Voltage Parameters.

# Step 6 – Choose Core and Bobbin Based on Output Power and Enter $A_{E}$ , $L_{E}$ , $A_{L}$ , BW, M, L, $N_{S}$

- When a core is selected, key parameters of the core are displayed, including  $A_{E}$ ,  $L_{E}$ ,  $A_{L}$ , BW and  $L_{G}$ . The default selected core is an EER35 and the default main output turns  $[N_{MAIN}]$  is 7 which is a typical core and turn set used for a 250-400 W PC application. EER28L is the smallest allowable core where  $N_{MAIN}$  can be set to 7 turns for +12 V main output without violating maximum allowable flux density. Select a core [CORE TYPE] and secondary turns  $[N_{MAIN}]$ , check [BM\_{MAX}] in the transformer design parameters section to determine whether flux density and current density are within safe limits. The spreadsheet will flag a warning if there is excessive flux density or current density for main transformer core.

- If a core of interest does not exist in the spreadsheet drop down list then enter specific core parameters from vendor data sheet directly into the spreadsheet.

- The default value is 7 turns for (+12 V) output. 7 turns creates a well centered ratio with N<sub>S2</sub> (+5 V) at 3 turns. N<sub>S2</sub> is computed by the spreadsheet to give the closest value possible to the [V<sub>OUT2</sub>] target. V<sub>OUT2\_ACTUAL</sub> and V<sub>BIAS\_ACTUAL</sub> are the actual computed values of those outputs relative to the selected value of V<sub>MAIN</sub> and the entered value of [V<sub>OUT2</sub>]. There is an option to override the default turns for [N<sub>S2</sub>], but it should be appreciated that the limitation of practical integral secondary turns values means that no solution will be perfect and that improved centering between V<sub>MAIN</sub> and V<sub>OUT2\_ACTUAL</sub> may not be possible by simply changing N<sub>S2</sub>.

- Enter number of primary layers. The default value is 3. Increasing layers should be avoided as it will increase the leakage inductance and possibly reduce current density (CMA), both aspects making the transformer less efficient.

- Enter the safety margin width. This parameter is half of the total primary plus secondary safety margin. For designs that have asymmetric 6 mm spacing on pin side and 3 mm spacing on non-pin side (a total of 9 mm), enter 4.5 mm in [BW].

- The items in the rows below are computed values for transformer design parameters including total primary turns  $[N_p]$  and peak flux density of core.  $[BM_{MAX}]$  is the nominal absolute peak flux excursion during normal operation.  $[BP_{MAX}]$  is the absolute peak flux excursion allowed by the L and RESET pin reset limiter circuit. The external clamp circuit, including the standard recovery diode DR1 (Figure 7) and the effective primary winding capacitance help set the core flux significantly negative at the end of the reset (off-time) cycle. This is why  $[BM_{MAX}]$  and  $[BP_{MAX}]$  are a lower value than [BM PK-PK] and [BP PK-PK].  $[BM_{MAX}]$  and  $[BP_{MAX}]$  are important parameters to determine flux density margin below core saturation during transient conditions. [BM PK-PK] and [BP PK-PK] are useful for determining core loss.

| TRANSFORMER CORE SELECTION |       |              |       |      |                                                                          |

|----------------------------|-------|--------------|-------|------|--------------------------------------------------------------------------|

| Core Type                  | EER35 |              |       |      | Selected core type                                                       |

| Core                       |       | EER35        |       | P/N: | PC40EER35-Z                                                              |

| Bobbin                     |       | EER35_BOBBIN |       |      | BEER-35-1116CPH                                                          |

| AE                         |       |              | 1.07  |      | Core Effective Cross Sectional Area                                      |

| LE                         |       |              | 9.08  |      | Core Effective Path Length                                               |

| AL                         |       |              | 2770  |      | Ungapped Core Effective Inductance                                       |

| BW                         |       |              | 26.1  |      | Bobbin Physical Winding Width                                            |

| M                          |       |              | 4.5   | mm   | Bobbin safety margin tape width (2 * M = Total Margin)                   |

| LG MAX                     |       |              | 0.002 | mm   | Maximum zero gap tolerance, default 2um                                  |

| L                          |       |              | 3.00  |      | Transformer primary layers (split primary recommended)                   |

| NMAIN                      |       |              | 7.0   |      | Main rounded turns                                                       |

| NS2                        |       |              | 3.0   |      | Vout2 rounded secondary turns (AC stacked winding)                       |

| NBIAS                      |       |              | 5     |      | VBias rounded turns (forward bias winding)                               |

| VOUT2 ACTUAL               |       |              | 4.9   |      | Approximate Output2 voltage of with NS2 = 3 turns (AC stacked secondary) |

| VBIAS_ACTUAL               |       |              | 16.2  | V    | Approximate Forward Bias Winding Voltage at VMIN with NB = 5 turns       |

Figure 11. Main Transformer Core Parameters.

| TRANSFORMER DESIGN PARAMETERS |  |       |          |                                                                     |

|-------------------------------|--|-------|----------|---------------------------------------------------------------------|

| NP                            |  | 89    |          | Primary rounded turns                                               |

| BM_MAX                        |  | 1791  | Gauss    | Max positive operating flux density at minimum switching frequency  |

| BM PK-PK                      |  | 2714  | Gauss    | Max peak-peak operating flux density at minimum switching frequency |

| BP_MAX                        |  | 2310  | Gauss    | Max positive flux density at Vmax (limited by DVMAX clamp)          |

| BP PK-PK                      |  | 3501  | Gauss    | Max peak-peak flux density at Vmax (limited by DVMAX clamp)         |

| LP MIN                        |  | 21.07 | mHenries | Minimum primary magnetizing inductance (assumes LG MAX=2um)         |

| IMAG                          |  | 0.122 | A        | Peak magnetizing current at minimum input voltage                   |

| OD_P                          |  | 0.58  |          | Primary wire outer diameter                                         |

| AWG_P                         |  | 23    | AWG      | Primary Wire Gauge (rounded to maximum AWG value)                   |

Figure 12. Main Transformer Flux Density and Other Parameters.

#### **Duty Cycle Values**

The rows in Figure 13 define typical and maximum duty cycle values. The three most significant values are:

$[\mathsf{DV}_{_{\mathsf{NOM}}}]$  is the normal operating duty cycle for continuous operation at nominal input voltage.

$[\mathrm{DV}_{\rm MIN}]$  is the duty cycle at the defined minimum input voltage where regulation can be maintained.  $[\mathrm{DV}_{\rm MIN}]$  is typically only at the end of the hold-up period as the input voltage collapses during AC shutdown.

$[{\rm D}_{\rm MAX}\!-\!V_{\rm NOM}]$  is the absolute maximum duty cycle allowed at nominal input voltage (limited by L and RESET pin limiter function).

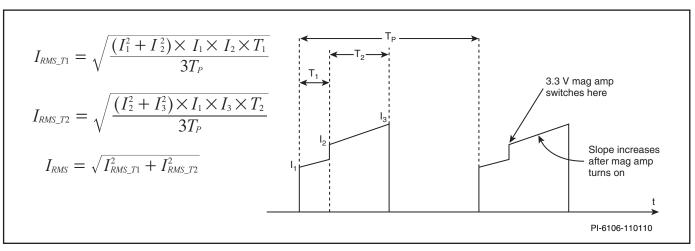

#### **Current Waveshape Parameters**

Figure 15 shows the key primary switch current parameters. The main primary switch path current  $[l_p]$  during the on-time cycle is measured at maximum input voltage and maximum continuous output power.  $[l_{P_{-}PEAK}]$  is the peak current during the defined peak output load  $[P_{OUT_{-}PEAK(MAIN)}]$ .  $[l_{PRMS(NOM)}]$  is the RMS current flowing through the main switches at maximum continuous output power.

The primary current waveform is complex when a mag amp post regulator is used. The mag amp will cause the primary current to step to a higher amplitude after the mag inductor has switched on (saturated), connecting the source potential of the +5 V winding to the mag amp output inductor current. The diagrams below show the approach to computing RMS current that accounts for the effect of mag amp post regulator on primary RMS current. As can be seen, the first step in computation is to divide the primary current waveform into two components, one of being which is main switch current before mag amp switches and the second component after the mag amp switches on. The RMS value of these two components are calculated independently, then added in quadrature for the total RMS current value of [I<sub>PRMSINOM</sub>].

Note: When using a buck post regulator, the current waveform is uniform, so this complication does not arise. If either  $[I_p]$  or  $[I_{p_p, PEAK}]$  are too high then a warning will show up in the text section that the current limit selection of HiperTFS device or device  $[I_{1,M}]$  configuration is not adequate for the

| DUTY CYCLE VALUES (REGULATION) |      |                                                         |

|--------------------------------|------|---------------------------------------------------------|

| DVMIN                          | 0.57 | Duty cycle at minimum DC input voltage                  |

| DVNOM                          | 0.45 | Duty cycle at nominal DC input voltage                  |

| DVMAX                          | 0.41 | Duty cycle at maximum DC input voltage                  |

| DOVOFF MIN                     | 0.26 | Duty cycle at over-voltage DC input voltage(DOVOFF_MIN) |

| MAXIMUM DUTY CYLE VALUES       |      |                                                         |

| DMAX_UVOFF_MIN                 | 0.62 | Max duty cycle clamp at VUVOFF_MIN                      |

| DMAX_VMIN                      | 0.60 | Max duty clamp cycle at VMIN                            |

| DMAX_VNOM                      | 0.58 | Max duty clamp cycle at VNOM                            |

| DMAX_VMAX                      | 0.52 | Max duty clamp cycle at VMAX                            |

| DMAX_OVOFFMIN                  | 0.33 | Max duty clamp cycle at VOVOFF_MAX                      |

Figure 13. HiperTFS Main Duty Cycle Parameters.

#### Figure 14. Primary Main Drain Current Waveshape Parameter.

required peak current. A higher current limit setting or a larger HiperTFS device will be advised.  $[I_{\text{PRMS(NOM)}}]$  is helpful in computing losses for the main switches

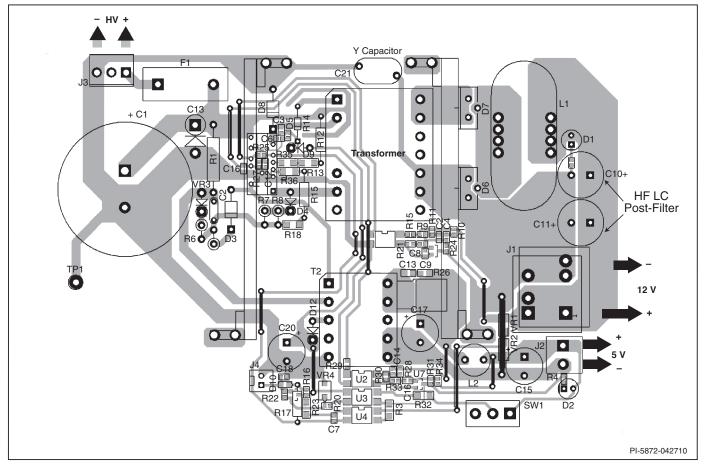

## **Transformer Construction**

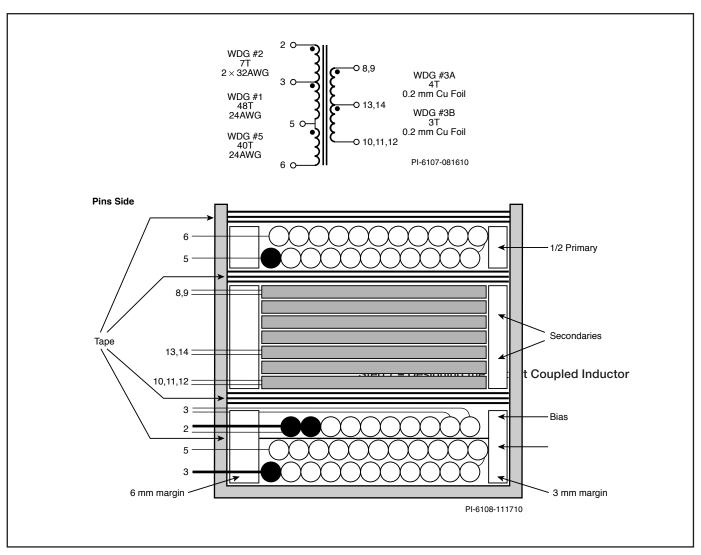

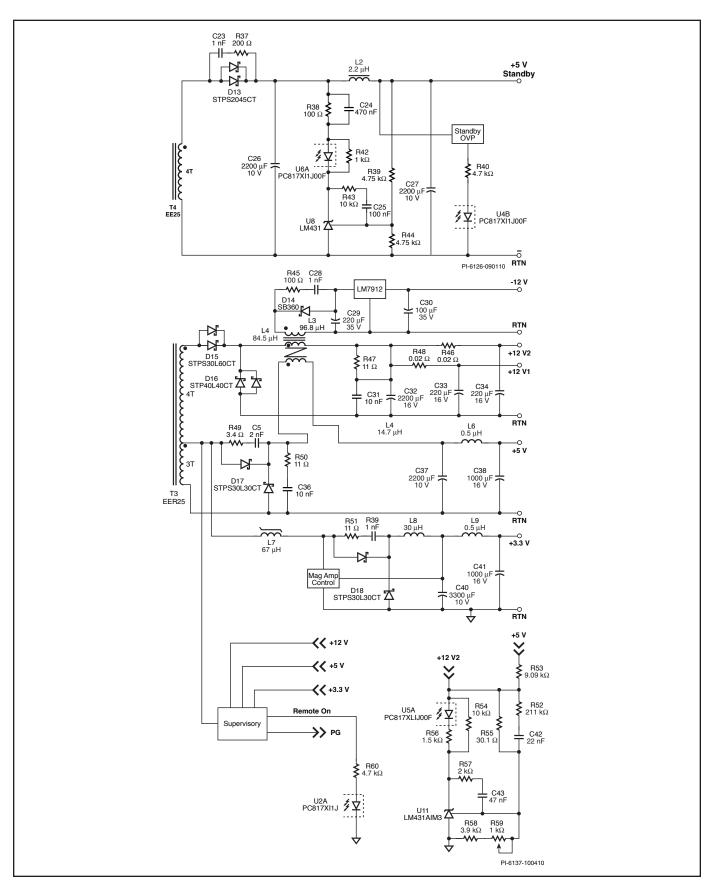

The spreadsheet will guide proper transformer design in terms of core size, turns, wire gauge and safety margin spacing. Figure 16 below (not included in spreadsheet) shows construction of a main transformer. Aspects of a typical main transformer design that are not shown in the spreadsheet are the use of split primary for improved coupling, and the use of foil, multistrand or litz wire for lower R<sub>AC</sub> associated losses. The secondary high current outputs are commonly foil construction. To determine required foil thickness use the RMS current information in secondary output parameters section (Figure 23) [ISFWDRMS] for the main output and [ISFWD2RMS] for [V<sub>OUT2</sub>]. Be sure to use appropriate thickness of foil or multi-strand to keep the current density above 200 CMA

| CURRENT WAVESHAPE PARAMETERS |  |      |   |                                                                    |

|------------------------------|--|------|---|--------------------------------------------------------------------|

| IP                           |  | 2.43 | A | Maximum peak primary current at maximum DC input voltage           |

| IP_PEAK                      |  | 2.43 | A | Peak primary current at Peak Output Power and max DC input voltage |

| IPRMS(NOM)                   |  | 1.36 | A | Nominal primary RMS current at nominal DC input voltage            |

Figure 15. HiperTFS Main Current Parameter.

Figure 16. 300 W Main Transformer Schematic and Construction.

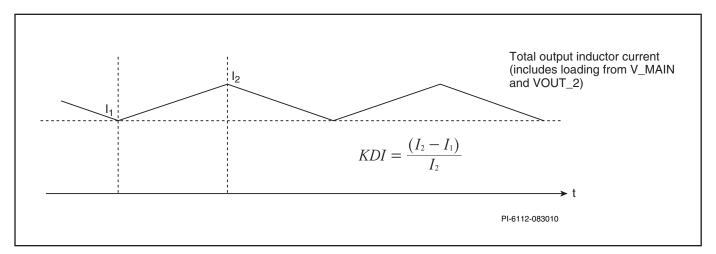

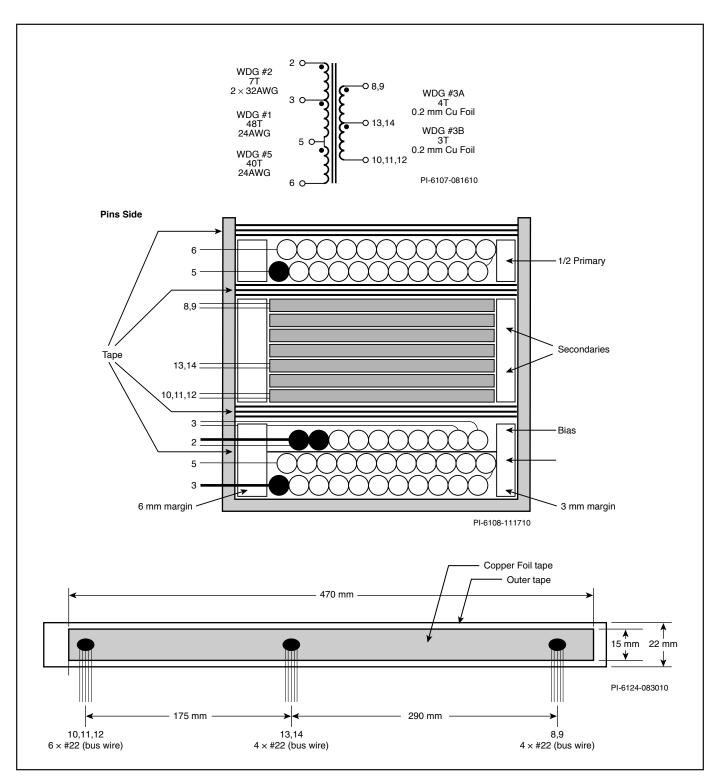

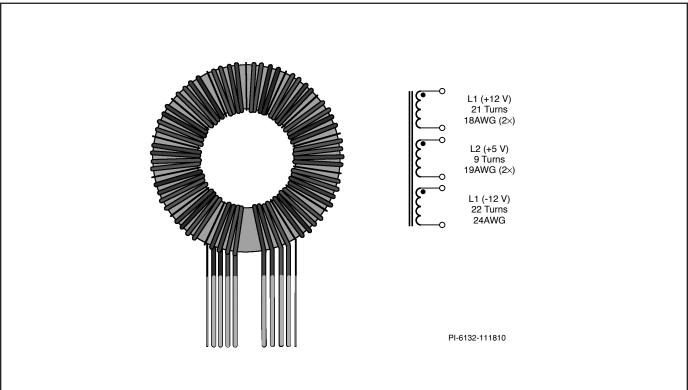

An essential part of designing a PC main converter is the design of the output coupled inductor. Core material and size, number of turns, and turns ratio are the major aspects of the inductor design. The output inductor should operate in continuous mode for the normal operating load range to keep good regulation between the +12 V and +5 V outputs. A coupled inductor is preferred as compared to discrete separate inductors, as it is much easier to maintain continuous conduction operation. since either output can force the core into continuous conduction mode. Powdered material such as Kool Mu or powdered iron also helps to maintain continuous conduction mode due to the non-linear A, nature of the material, allowing the inductance to be significantly higher at lighter loads than at high load. At higher loads it is important to know the value for ripple factor (KDI) as shown in Figure 17. Excessively high ripple will cause the converter to run less efficiently from associated RMS current losses in primary converter switches, main transformer windings, output inductor windings and output capacitors. Restricting core loss of the output inductor is also an significant factor in improving efficiency. As an example, for Kool Mu, the AC peak flux density should be kept below [BAC IND] 500 gauss.

When designing a coupled inductor, first choose the type of core material to be used. Kool Mu (Sendust) is usually the material selected for high efficiency designs. Powdered iron is generally chosen when cost is more of a factor than efficiency in overall design goals. There is an option to select ferrite material, although this material is not normally used as a coupled inductor core at 66 kHz.

#### Step-by-Step Procedure

- Select core material in [Core Type] from the drop down menu (optimal core size is automatically selected). Notice that there is a separate section in the spreadsheet are for powder core (Sendust and KoolMu) and ferrite computations.

- The spreadsheet automatically selects core [Core] and turns [Turns] to give a minimum core size for a KDI (ripple current factor) of approximately 0.26 and an AC flux density [BAC\_IND] below 500 Gauss.

- If another core size is desired, then enter the core size in [Core]. When selecting a core other than the automatically selected size, check for excessive AC flux density warning [BAC\_IND]. Also make sure KDI is below 0.5 and the layer build is below 2.

- Inductance [LMAIN\_ACTUAL] and KDI of LMAIN can be changed by changing the number of turns [NMAIN\_INDUC-TOR] of the main output inductor winding. The default turns for the coupled inductor is 3 times the associated main transformer secondary turns. To change inductor turns, enter a multiplier value [INDUCTOR TURNS MULTIPLIER] other than the default 3X. When selecting a multiplier other than the default value, check for an excessive AC flux density warning [BAC\_IND]. Also make sure KDI is below 0.5 (to maintain continuous inductor operation) and the layer build is below 2.

Figure 17. Secondary Coupled Inductor Current Waveshape.

| OUTPUT INDUCTOR OUTPUT PARAMETERS |      |                  |        |                                                            |

|-----------------------------------|------|------------------|--------|------------------------------------------------------------|

| KDI_ACTUAL                        |      | 0.28             |        | Current ripple factor of combined Main and Output2 outputs |

| Core Type                         | Auto | Kool Mu 125u     |        | Select core type                                           |

| Core                              | Auto | 77930(O.D)=27.7) |        | Coupled Inductor - Core size                               |

|                                   |      |                  |        |                                                            |

| AE                                |      | 65.4             | mm^2   | Core Effective Cross Sectional Area                        |

|                                   |      |                  |        |                                                            |

| LE                                |      | 63.5             | mm     | Core Effective Path Length                                 |

| AL                                |      | 113.0            | nH/T^2 | Ungapped Core Effective Inductance                         |

| BW                                |      | 44.3             | mm     | Bobbin Physical Winding Width                              |

| VE                                |      | 4150.0           | mm^3   |                                                            |

Figure 18. Output Coupled Inductor Parameter.

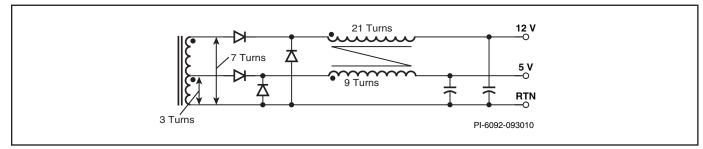

Figure 19. Coupled Inductor and Main Transformer Typical Turns for 5 V and 12 V Outputs.

| Powder cores (Sendust and Powdered Iron) Cores |        |       |                                                                               |

|------------------------------------------------|--------|-------|-------------------------------------------------------------------------------|

| MUR                                            | 90.0   |       | Relative permiability of material                                             |

| н                                              | 84.9   | AT/cm | Magnetic field strength                                                       |

| MUR_RATIO                                      | 0.31   |       | Percent of permiability as compared to permiability at H = 0 AT/cm            |

| LMAIN_ACTUAL                                   | 15.7   | uH    | Estimated inductance of main output at full load                              |

| LMAIN_0bias                                    | 49.8   | uH    | Estimated inductance of main output with 0 DC bias                            |

| LOUT2                                          | 2.9    | uH    | Estimated inductance of auxilliary output at full load                        |

| BM_IND                                         | 2931.7 | Gauss | DC component of flux density                                                  |

| BAC_IND                                        | 444.6  | Gauss | AC component of flux density                                                  |

| Turns                                          |        |       |                                                                               |

|                                                |        |       | Multiplier factor between main number of turns in transformer and inductor    |

| INDUCTOR TURNS MULTIPLIER                      | 3.0    |       | (default value = 3)                                                           |

| NMAIN_INDUCTOR                                 | 21.0   |       | Main output inductor number of turns                                          |

| NOUT2_INDUCTOR                                 | 9.0    |       | Output 2 inductor number of turns                                             |

| NOUT4_INDUCTOR                                 | 22.0   |       | Bias output inductor number of turns (for bias or control circuit VDD supply) |

Figure 20. Output Coupled Inductor Flux Density.

- Wire parameters section of the spreadsheet are common to both powder core and ferrite designs.

- There is an option to change wire gauge and number of strands. If foil is used, then be sure cross sectional area will result in no less than 200 CMA at maximum load.

| Wire Parameters            |      |       |        |                                                                                |

|----------------------------|------|-------|--------|--------------------------------------------------------------------------------|

| Total number of layers     |      | 1.67  |        | Total number of layers for chosen toroid                                       |

| IRMS_MAIN                  |      | 15.1  | A      | RMS current through main inductor windings                                     |

| IRMS_AUX                   |      | 15.2  | A      | RMS current through aux winding                                                |

| AWG_MAIN                   |      | 17.0  | AWG    | Main inductor winidng wire gauge                                               |

| OD_MAIN                    |      | 1.2   | mm     | Main winding wire gauge outer diameter                                         |

| FILAR_MAIN                 | <br> | 2.0   |        | Number of parallel strands for main output                                     |

| RDC_MAIN                   |      | 6.9   | mohm   | Reisstance of wire for main inductor winding                                   |

| AC Resistance Ratio (Main) |      | 4.0   |        | Ratio of total resistance (AC + DC) to the DC resistance (using Dowell curves) |

| CMA_MAIN                   |      | 273.1 | CMA    | Cir mils per amp for main inductor winding                                     |

| J_MAIN                     |      | 12.8  | A/mm^2 | Current density in main inductor winding                                       |

| AWG_AUX                    |      | 17.0  | AWG    | Aux winding wire gauge                                                         |

| OD_MAIN                    |      | 1.2   | mm     | Auxilliary winding wire gauge outer diameter                                   |

| FILAR_AUX                  |      | 2.0   |        | Number of parallel strands for aux output                                      |

| RDC_AUX                    |      | 3.0   | mohm   | Reisstance of wire for aux inductor winding                                    |

| AC Resistance Ratio (Aux)  |      | 1.31  |        | Ratio of total resistance (AC + DC) to the DC resistance (using Dowell curves) |

| CMA_AUX                    |      | 273.1 | CMA    | Cir mils per amp for main inductor winding                                     |

| J_AUX                      |      | 13.0  | A/mm^2 | Current density in auxilliary winding                                          |

Figure 21. Output Coupled Inductor RMS Currents.

• This section provides inductor core and winding losses estimates at maximum output power.

| Estimated Power Loss |  |     |   |                                       |

|----------------------|--|-----|---|---------------------------------------|

| PCOPPER_MAIN         |  | 1.6 | W | Copper loss in main inductor windinig |

| PCOPPER_AUX          |  | 0.7 | W | Copper loss in aux inductor winidgs   |

| PCORE                |  | 0.4 | W | Total core loss                       |

| PTOTAL               |  | 2.6 | W | Total losses in output choke          |

Figure 22. Estimated Coupled Inductor Losses.

This section gives information concerning maximum voltage and current stress for output rectifiers. Look here to determine the minimum acceptable output diode voltage rating.

| SECONDARY OUTPUT PARAMETERS |            |          |   |                                                                |

|-----------------------------|------------|----------|---|----------------------------------------------------------------|

| ISFWDRMS                    |            | 11.47    | A | Max. fwd sec. RMS current (at DVNOM)                           |

| ISFWD2RMS                   |            | 11.47    | A | Max. fwd sec. RMS current (at DVNOM)                           |

|                             |            |          |   |                                                                |

| ISCATCHRMS                  |            | 12.66    | A | Max. catch sec. RMS current (at DVNOM)                         |

| ISCATCH2RMS                 |            | 12.66    | A | Max. catch sec. RMS current (at DVNOM)                         |

|                             |            |          |   |                                                                |

| IDAVMAINF                   |            | 8.59     | A | Maximum average current, Main rectifier (single device rating) |

| IDAVMAINC                   |            | 8.89     | A | Maximum average current, Main rectifier (single device rating) |

| IDAVOUT2F                   |            | 8.59     | A | Maximum average current, Main rectifier (single device rating) |

| IDAVOUT2C                   |            | 8.89     | A | Maximum average current, Main rectifier (single device rating) |

|                             |            |          |   |                                                                |

| IRMSMAIN                    |            | 1.20     | A | Maximum RMS current, Main output capacitor                     |

| IRMSOUT2                    |            | 1.20     | A | Maximum RMS current, Out2 output capacitor                     |

|                             | % Derating |          |   |                                                                |

| VPIVMAINF                   | 100%       | 44.8     | V | Main Forward Diode peak-inverse voltage (at VDSOP)             |

| VPIVMAINC                   | 100%       | 33.0     | V | Main Catch Diode peak-inverse voltage (at VOVOFF_MAX)          |

| VPIVOUT2F                   | 100%       | 19.2     | V | Output2 Forward Diode peak-inverse voltage (at VDSOP)          |

| VPIVOUT2C                   | 100%       | 14.2     | V | Output2 Catch Diode peak-inverse voltage (at VOVOFF_MAX)       |

| VPIVB                       | 100%       | <br>32.0 | V | Bias output rectifier peak-inverse voltage (at VDSOP)          |

Figure 23. Secondary RMS Currents and Output Diode Voltage Ratings.

# **Standby Section**

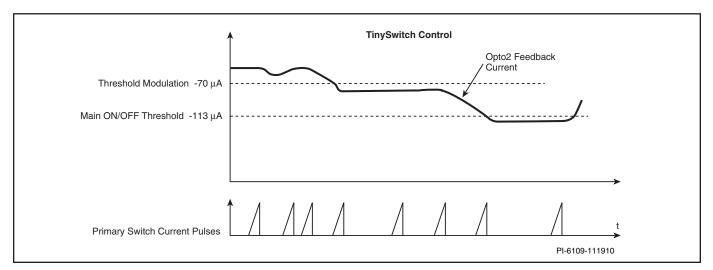

The standby section of HiperTFS is essentially a TinySwitch device and follows the design procedure for TinySwitch-III with a few exceptions:

- I<sub>LIM</sub> selection is implemented by selecting a value of pull-up resistor from the enable pin to the bypass pin (rather than selection of bypass capacitor value as is done for TinySwitch-III).

- 2. UV lockout is sensed through LINE-SENSE pin rather than through ENABLE pin

- 3. Reset of OV latch is done through pulling LINE-SENSE pin low or when L pin current falls below 10  $\mu$ A.

- 4. The standby converter in HiperTFS has input line voltage compensation added to overpower threshold which keeps output overpower limit threshold relatively constant with respect to line.

#### Step 1 – AC Input and Output Voltage and Current

- Enter input voltage range [VAC<sub>MIN</sub>] and [VAC<sub>MAX</sub>].

- Enter output voltage [VO<sub>SB</sub>] and output current [IO<sub>SB</sub>].

- Enter peak output current [IO(SB)(PK)].

- Enter expected efficiency [η].

- Inputs [Z] and  $[t_{\rm c}]$  are usually left to the default values.

| HiperTFS STANDBY SECTION (FLYBACK STAGE) |      |       |    |                                                                                   |

|------------------------------------------|------|-------|----|-----------------------------------------------------------------------------------|

| ENTER APPLICATION VARIABLES              |      |       |    |                                                                                   |

| VACMIN                                   | 85   |       | v  | Minimum AC Input Voltage                                                          |

| VACMAX                                   | 265  |       | V  | Maximum AC Input Voltage                                                          |

| fL                                       | 50   |       | Hz | AC Mains Frequency                                                                |

| VO_SB                                    | 5.00 |       | V  | Output Voltage (at continuous power)                                              |

| IO_SB                                    | 2.00 |       | A  | Power Supply Output Current (corresponding to peak power)                         |

| IO_SB_PK                                 | 3.50 |       |    |                                                                                   |

| POUT_SB                                  |      | 10    | W  | Continuous Output Power                                                           |

| POUT_SB_TOTAL                            |      | 10.32 | W  | Total Standby power (Includes Bias winding power)                                 |

| POUT_SB_PK                               |      | 17.5  | W  | Peak Standby Output Power                                                         |

| n                                        | 0.70 |       |    | Efficiency Estimate at output terminals. Under 0.7 if no better data available    |

|                                          | _    |       |    | Z Factor. Ratio of secondary side losses to the total losses in the power supply. |

| Ζ                                        | 0.50 |       |    | Use 0.5 if no better data available                                               |

| tC                                       | 3.00 |       | ms | Bridge Rectifier Conduction Time Estimate                                         |

Figure 24. Standby Supply Design Parameters.

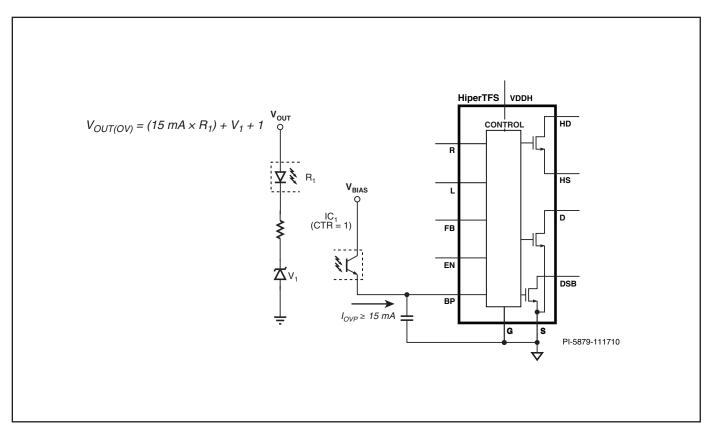

# Step 2 – Selecting Current Limit, $\mathrm{V}_{_{\mathrm{OR}}}$ and Bias Winding

- Depending on output power select one of four current limit options LOW, RED, STD, INC. Once current limit has been selected I<sub>LIM</sub> value are displayed.

- Select  $V_{OR}$ . 90 V is default setting which is usually the most efficient design. Selecting a higher value of  $V_{OR}$  can cause higher clamp losses. A  $V_{OR}$  lower than 90 V will increase the peak reverse voltage across output rectifier.

- Note that the standby converter is switching at twice the frequency of the main converter. (i.e.  $f_{s_{B}} = 132$  kHz).

- The standby transformer bias winding  $[V_B]$  is used to operate a primary side auxiliary supply. This feeds a +12 V regulator that supplies a number of primary side circuits including typically providing operating current to the PFS boost stage. The default value of +16 V gives adequate headroom for +12 V bias regulator.

- UVLO section shows expected turn on threshold for standby  $[V_{\text{UVIACTUAL}}]$  for the given line sense resistor value  $[R_{LS}]$ .

| ENTER HiperTFS STANDBY VARIABLES |     |                   |        |                                                                                  |

|----------------------------------|-----|-------------------|--------|----------------------------------------------------------------------------------|

|                                  |     |                   |        | Enter "LOW" for low current limit, "RED" for reduced current limit (sealed       |

|                                  |     | Increased Current |        | adapters), "STD" for standard current limit or "INC" for increased current limit |

| Select Current Limit             | INC | Limit             |        | (peak or higher power applications)                                              |

| ILIM_MIN                         |     | 0.698             | A      | Minimum Current Limit                                                            |

| ILIM_TYP                         |     | 0.750             | A      | Typical Current Limit                                                            |

| ILIM_MAX                         |     | 0.803             | A      | Maximum Current Limit                                                            |

| R(EN)                            |     | 137.0             | k-ohms | Enable pin resistor                                                              |

| fSmin                            |     | 124000            | Hz     | Minimum Device Switching Frequency                                               |

|                                  |     |                   |        | I^2f (product of current limit squared and frequency is trimmed for tighter      |

| I^2fmin                          |     | 66.83             | A^2kHz | tolerance)                                                                       |

| VOR                              |     | 90                | V      | Reflected Output Voltage (VOR < 135 V Recommended)                               |

| VDS                              |     | 10                | V      | HiperTFS Standby On State Drain to Source Voltage                                |

| VD_SB                            |     | 0.5               | V      | Output Winding Diode Forward Voltage Drop                                        |

| KP                               |     | 0.65              |        | Ripple to Peak Current Ratio (KP < 6)                                            |

| KP_TRANSIENT                     |     | 0.33              |        | Transient Ripple to Peak Current Ratio. Ensure KP_TRANSIENT > 0.25               |

Figure 25. HiperTFS Standby Current Limit and Reflected Voltage.

| ENTER BIAS WINDING VARIABLES |  |       |        |                                                   |

|------------------------------|--|-------|--------|---------------------------------------------------|

| VB                           |  | 16.00 | V      | Bias Winding Voltage                              |

| IB                           |  | 20.00 | mA     | Bias winding Load current                         |

| PB                           |  | 0.32  | W      | Bias winidng power                                |

| VDB                          |  | 0.70  |        | Bias Winding Diode Forward Voltage Drop           |

| NB                           |  | 12.15 |        | Bias Winding Number of Turns                      |

| VZOV                         |  | 22.00 | V      | Over Voltage Protection zener diode voltage.      |

| UVLO VARIABLES               |  |       |        |                                                   |

| RLS                          |  | 4.03  | M-Ohms | Line sense resistor (from Main converter section) |

| V_UV_ACTUAL                  |  | 103   | V      | Typical DC start-up voltage                       |

Figure 26. Standby Bias Winding Voltage and Input Undervoltage.

#### Step 3 – Standby Transformer Design

- Select desired core [Core Type] from drop down menu. The default core is EE25 (El25) which is adequate for up to 20 W. EE19, EEL19, EE22 are also commonly used for lower power.

- Select secondary turns [N<sub>s</sub>]. Four turns trifilar wound gives best efficiency for +5 V output.

- If desired core is not in drop down list then enter core and bobbin parameters directly into [A<sub>F</sub>] [L<sub>F</sub>] [A<sub>I</sub>] [BW].

#### **Transformer Design Parameters**

Key parameters to check are:

- [LP<sub>SB</sub>] Primary inductance is a key parameter in determining output power.

- [B<sub>M</sub>] Maximum flux density should be below 3000 Gauss.

- [CMA] Current density of windings at max continuous output power should be above 200 CMA to avoid excessive thermal rise of transformer.

| ENTER TRANSFORMER CORE/CONSTRUCTION VARIA |      |             |        |        |                                                                               |

|-------------------------------------------|------|-------------|--------|--------|-------------------------------------------------------------------------------|

| Core Type                                 | EE25 |             | EE25   |        | Enter Transformer Core                                                        |

| Core                                      |      | EE25        |        | P/N:   | PC40EE25-Z                                                                    |

| Bobbin                                    |      | EE25_BOBBIN |        | P/N:   | EE25_BOBBIN                                                                   |

| AE                                        |      |             | 0.404  | cm^2   | Core Effective Cross Sectional Area                                           |

| LE                                        |      |             | 7.34   | cm     | Core Effective Path Length                                                    |

| AL                                        |      |             | 1420   | nH/T^2 | Ungapped Core Effective Inductance                                            |

| BW                                        |      |             | 10.2   | mm     | Bobbin Physical Winding Width                                                 |

| M                                         |      |             | 0      | mm     | Safety Margin Width (Half the Primary to Secondary Creepage Distance)         |

| L                                         |      |             | 2      |        | Number of Primary Layers                                                      |

| NS_SB                                     |      |             | 4      |        | Number of Secondary Turns                                                     |

| DC INPUT VOLTAGE PARAMETERS               |      |             |        |        |                                                                               |

| VMIN_SB                                   |      |             | 114.52 | V      | Minimum DC Input Voltage                                                      |

| VMAX_SB                                   |      |             | 374.77 | V      | Maximum DC Input Voltage                                                      |

| CURRENT WAVEFORM SHAPE PARAMETERS         |      |             |        |        |                                                                               |

| DMAX_SB                                   |      |             | 0.46   |        | Duty Ratio at full load, minimum primary inductance and minimum input voltage |

| IAVG                                      |      |             | 0.24   | A      | Average Primary Current                                                       |

| IP_SB                                     |      |             | 0.70   | A      | Minimum Peak Primary Current                                                  |

| IR_SB                                     |      |             | 0.45   | A      | Primary Ripple Current                                                        |

| IRMS_SB                                   |      |             | 0.38   | A      | Primary RMS Current                                                           |

Figure 27. Standby Transformer Selection.

| TRANSFORMER PRIMARY DESIGN PARAMETERS   |        |           |                                                                               |

|-----------------------------------------|--------|-----------|-------------------------------------------------------------------------------|

|                                         |        |           | Typical Primary Inductance. +/- 10% to ensure a minimum primary inductance of |

| LP SB                                   | 799.10 | uH        | 726 uH                                                                        |

| LP TOLERANCE                            | 10     | %         | Primary inductance tolerance                                                  |

| NP SB                                   | 65     |           | Primary Winding Number of Turns                                               |

| ALG                                     | 187    | nH/T^2    | Gapped Core Effective Inductance                                              |

| BM                                      | 2425   | Gauss     | Maximum Operating Flux Density, BM<3000 is recommended                        |

| BAC                                     | 785    | Gauss     | AC Flux Density for Core Loss Curves (0.5 X Peak to Peak)                     |

| ur                                      | 2053   |           | Relative Permeability of Ungapped Core                                        |

| LG                                      | 0.24   | mm        | Gap Length (Lg > 0.1 mm)                                                      |

| BWE                                     | 20.4   | mm        | Effective Bobbin Width                                                        |

| OD                                      | 0.31   | mm        | Maximum Primary Wire Diameter including insulation                            |

| INS                                     | 0.05   | mm        | Estimated Total Insulation Thickness (= 2 * film thickness)                   |

| DIA                                     | 0.26   | mm        | Bare conductor diameter                                                       |

| AWG                                     | 30     | AWG       | Primary Wire Gauge (Rounded to next smaller standard AWG value)               |

| CM                                      | 102    | Cmils     | Bare conductor effective area in circular mils                                |

| CMA                                     | 265    | Cmils/Amp | Primary Winding Current Capacity (200 < CMA < 500)                            |

| TRANSFORMER SECONDARY DESIGN PARAMETERS |        |           |                                                                               |

| Lumped parameters                       |        |           |                                                                               |

| ISP                                     | 11.41  | A         | Peak Secondary Current                                                        |

| ISRMS                                   | 6.76   | A         | Secondary RMS Current                                                         |

| IRIPPLE                                 | 6.45   | A         | Output Capacitor RMS Ripple Current                                           |

| CMS                                     | 1351   | Cmils     | Secondary Bare Conductor minimum circular mils                                |

| AWGS                                    | 18     | AWG       | Secondary Wire Gauge (Rounded up to next larger standard AWG value)           |

| VOLTAGE STRESS PARAMETERS               |        |           |                                                                               |

|                                         |        |           | Maximum Drain Voltage Estimate (Assumes 20% zener clamp tolerance and an      |

| VDRAIN                                  | 584    | V         | additional 10% temperature tolerance)                                         |

| PIVS                                    | 28     | V         | Output Rectifier Maximum Peak Inverse Voltage                                 |

Figure 28. Standby Transformer Parameter.

|                         | Output Power Range<br>(W) | Core Size                       | Core Material   | Source        |

|-------------------------|---------------------------|---------------------------------|-----------------|---------------|

|                         | 150-300                   | EER28                           | Ferrite         | TDK, Mag Inc. |

| Main Transformer        | 150-300                   | EDT34                           | Ferrite         | TDK, Mag Inc. |

|                         | 300-450                   | EER35                           | Ferrite         | TDK, Mag Inc. |

|                         | 4-8                       | EE16                            | Ferrite         | TDK, Mag Inc. |

| Standby Transformer     | 8-15                      | EE19                            | Ferrite         | TDK, Mag Inc. |

|                         | 12-20                     | EER28<br>EDT34<br>EER35<br>EE16 | Ferrite         | TDK, Mag Inc. |

|                         | 150-300                   | 27.7 (OD)                       | Sendust, Koolmu | Mag Inc. CSC  |

|                         | 300-450                   | 33.8 (OD)                       | Sendust, Koolmu | Mag Inc. CSC  |

| Coupled Output Inductor | 150-300                   | 33.0 (OD) (T130-52)             | Powdered Iron   | Micrometals   |

|                         | 300-450                   | 38.4 (OD) (T150-52)             | Powdered Iron   |               |

Table 2. Common Cores Sizes and Sources.

# External Circuit Design and Circuit Options for HiperTFS

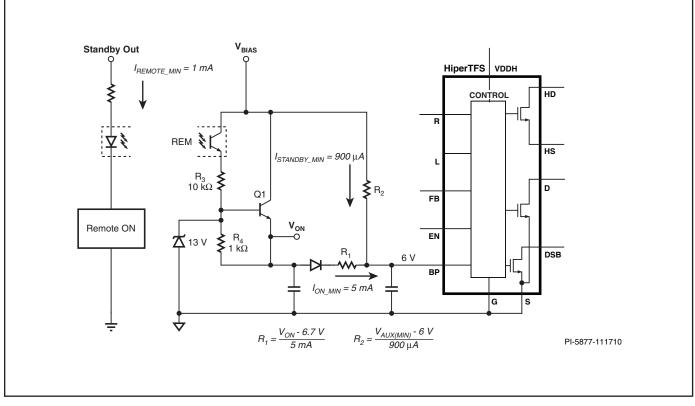

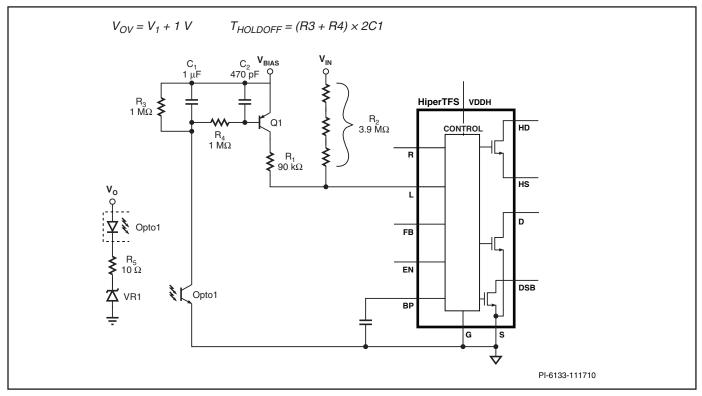

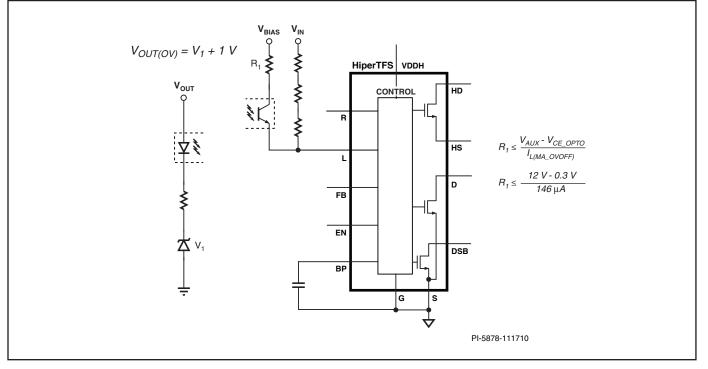

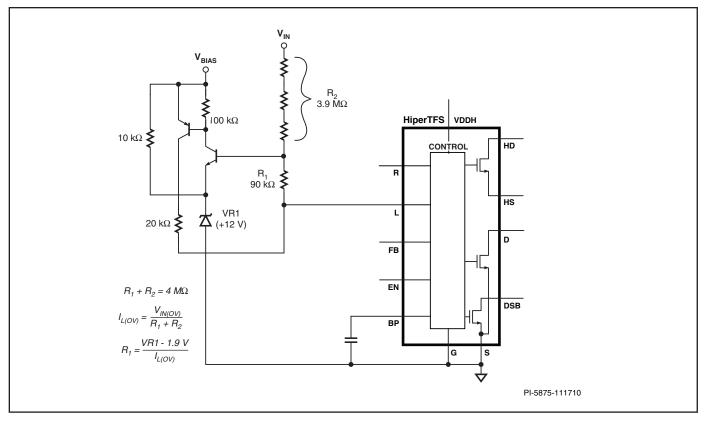

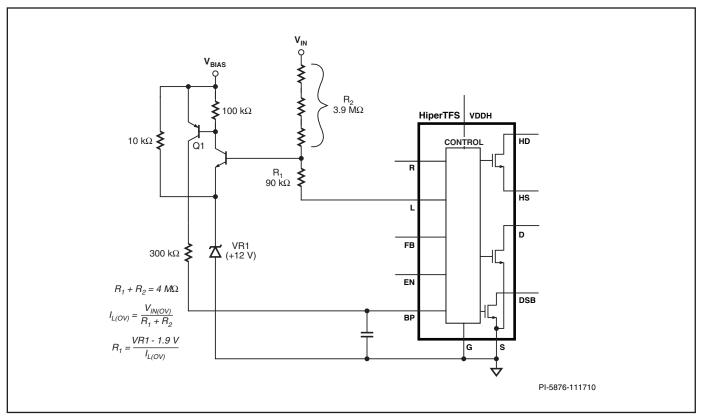

#### Remote-On and Standby Bias

When the standby converter turns on and achieves regulation it provides an auxiliary bias  $[V_{\text{BIAS}}]$  for primary side control circuits. The primary bias is the source for the remote-on output  $(V_{\text{ON}})$  which is a +12 V regulated output. The external circuit configuration is shown below in Figure 29.

#### **Design and Operation**

The initial application of AC will provide a DC input to both main and standby converters. The HiperTFS high-voltage internal current source tab will then charge the BYPASS (BP) pin to 5.8 V and the standby converter will start to switch. When input reaches [V<sub>UV</sub>] the standby supply will power up while the main converter remains off. When the standby output reaches regulation there will also be a bias [V<sub>BIAS</sub>] available from the standby converter.  $[V_{AUX}]$  will then provide bias to the BYPASS pin through R2 which will bring the BP voltage up to 6 V and turn off the internal high voltage current source which allows the standby converter to operate more efficiently. When the standby converter is on and in regulation, a remote-on (power-on) command can be made from the secondary side by turning the opto LED (REM) on which turns on Q1. The emitter of Q1 then provides 12.6 V which is sufficient to cause 5 mA to flow into the BYPASS pin. This BYPASS pin current is sensed internally by HiperTFS and triggers the main converter to start its turn-on sequence. Details of turn on sequence will be described in high-side driver section.

Note:  $\rm V_{_{ON}}$  voltage can be adjusted by modifying  $\rm V_{_{ZENER}}$  (typically 13 V).

Figure 29. Remote-ON and Standby Bias.

High-Side Drive Operation and Bias

As described in the previous section, when there is an initial Remote-on command, 12 V power is applied to the HiperTFS BYPASS pin, allowing the main converter to turn on. It does so in a series of steps. Referring to Figure 31, first the MAIN DRAIN pin of the bottom MOSFET is pulled low for 12 ms. This allows sufficient time for C1 to be bootstrap charged from the standby bias output through CR1. The voltage across C1 feeds the high-side driver bias voltage into C2 through R1 which is shunt regulated to +12 V by high-side operating voltage (VDDH) pin internal shunt regulator. The main converter will then start high-side and low-side switching 12 ms after receiving the remote-on command. Output voltages will rise at a rate determined by the built in duty cycle soft-start until the secondary main feedback regulator controls the duty cycle via the FEEDBACK pin of the HiperTFS. Once switching begins the external bias source for main high-side operating voltage pin (VDDH) is derived from a forward phased winding off the main transformer.

Figure 30. Supply Start-Up Sequence by Remote-ON

Figure 31. High-Side Bias.

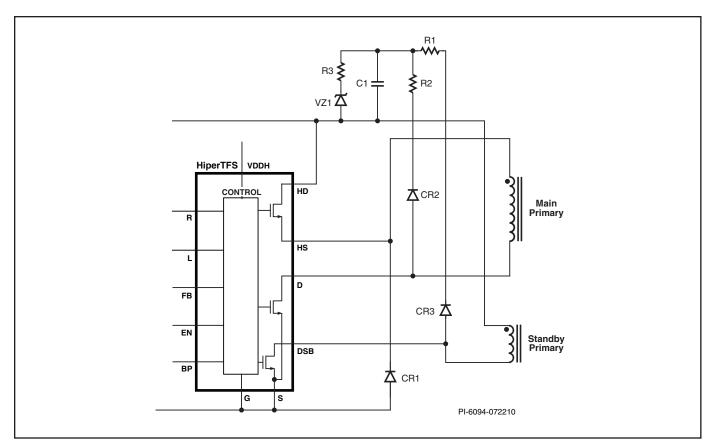

# Primary Clamp Circuit

The diagram below shows the standard clamp-to-rail configuration. The clamp energy of both the primary main winding magnetizing and leakage inductance and standby primary winding leakage inductance are routed through CR2 and CR3 to Zener clamp VZ1 and C1.

R1, R2, and R3 are damping resistors. Diodes CR2 and CR3 are standard slow recovery diodes such as 1N4007G which allow recycling of the leakage and magnetizing energy from C1.